|

|

|

|

|

|

| www.ti.com |

|

SRIO Functional Description |

|

|

|

|

|

|

| |

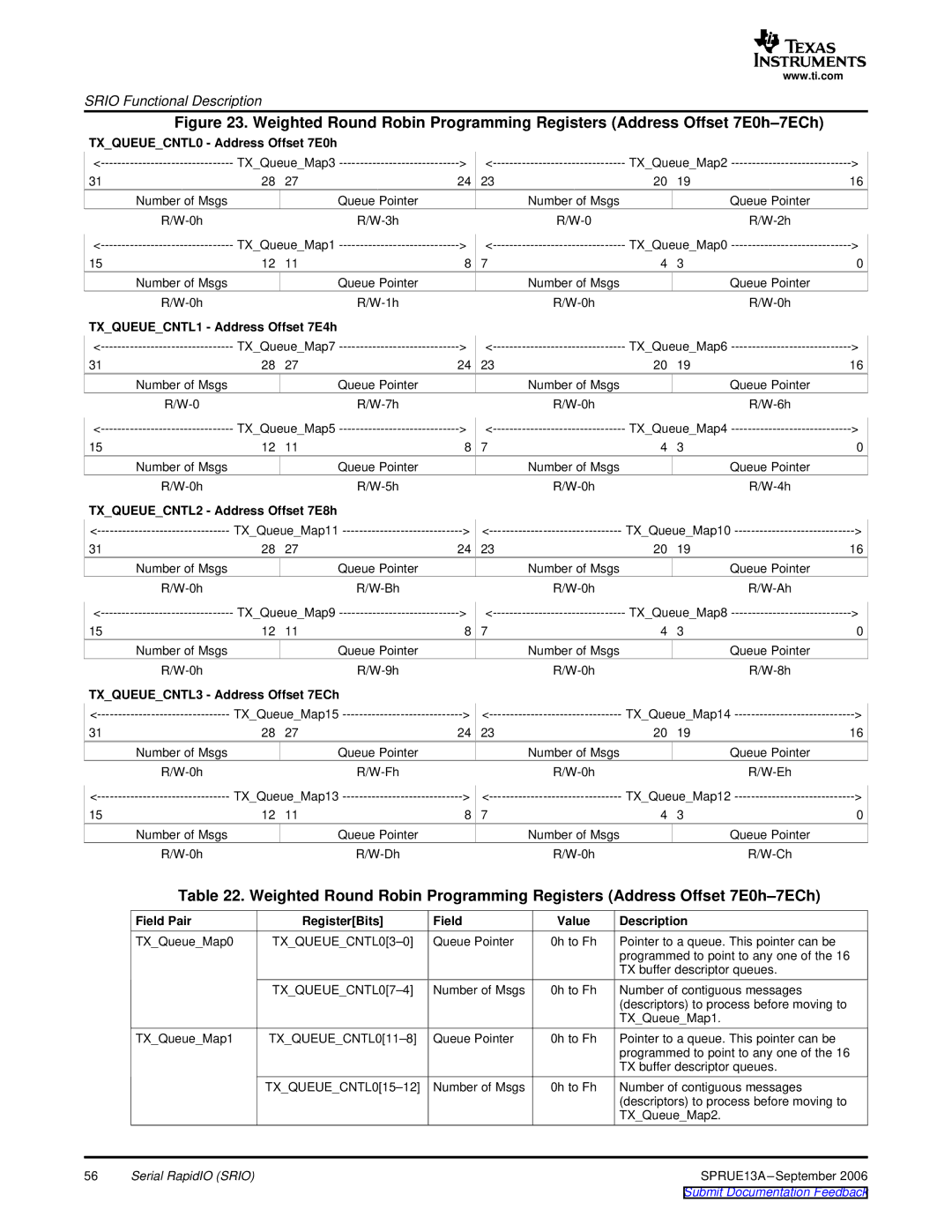

Figure 23. Weighted Round Robin Programming Registers (Address Offset |

| |||||||

TX_QUEUE_CNTL0 - Address Offset 7E0h |

|

|

|

|

|

| ||

TX_Queue_Map3 | > | TX_Queue_Map2 | > | |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 |

| 16 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_Queue_Map1 | > | TX_Queue_Map0 | > | |||||

15 | 12 | 11 | 8 | 7 | 4 | 3 |

| 0 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_QUEUE_CNTL1 - Address Offset 7E4h |

|

|

|

|

|

| ||

TX_Queue_Map7 | > | TX_Queue_Map6 | > | |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 |

| 16 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_Queue_Map5 | > | TX_Queue_Map4 | > | |||||

15 | 12 | 11 | 8 | 7 | 4 | 3 |

| 0 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_QUEUE_CNTL2 - Address Offset 7E8h |

|

|

|

|

|

| ||

TX_Queue_Map11 | > | TX_Queue_Map10 | > | |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 |

| 16 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_Queue_Map9 | > | TX_Queue_Map8 | > | |||||

15 | 12 | 11 | 8 | 7 | 4 | 3 |

| 0 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_QUEUE_CNTL3 - Address Offset 7ECh |

|

|

|

|

|

| ||

TX_Queue_Map15 | > | TX_Queue_Map14 | > | |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 |

| 16 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_Queue_Map13 | > | TX_Queue_Map12 | > | |||||

15 | 12 | 11 | 8 | 7 | 4 | 3 |

| 0 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

Table 22. Weighted Round Robin Programming Registers (Address Offset

| Field Pair | Register[Bits] | Field | Value | Description |

| TX_Queue_Map0 |

| Queue Pointer | 0h to Fh | Pointer to a queue. This pointer can be |

|

|

|

|

| programmed to point to any one of the 16 |

|

|

|

|

| TX buffer descriptor queues. |

|

|

| Number of Msgs | 0h to Fh | Number of contiguous messages |

|

|

|

|

| (descriptors) to process before moving to |

|

|

|

|

| TX_Queue_Map1. |

| TX_Queue_Map1 |

| Queue Pointer | 0h to Fh | Pointer to a queue. This pointer can be |

|

|

|

|

| programmed to point to any one of the 16 |

|

|

|

|

| TX buffer descriptor queues. |

|

|

| Number of Msgs | 0h to Fh | Number of contiguous messages |

|

|

|

|

| (descriptors) to process before moving to |

|

|

|

|

| TX_Queue_Map2. |

56 | Serial RapidIO (SRIO) |

|

|

| SPRUE13A |