www.ti.com

SRIO Registers

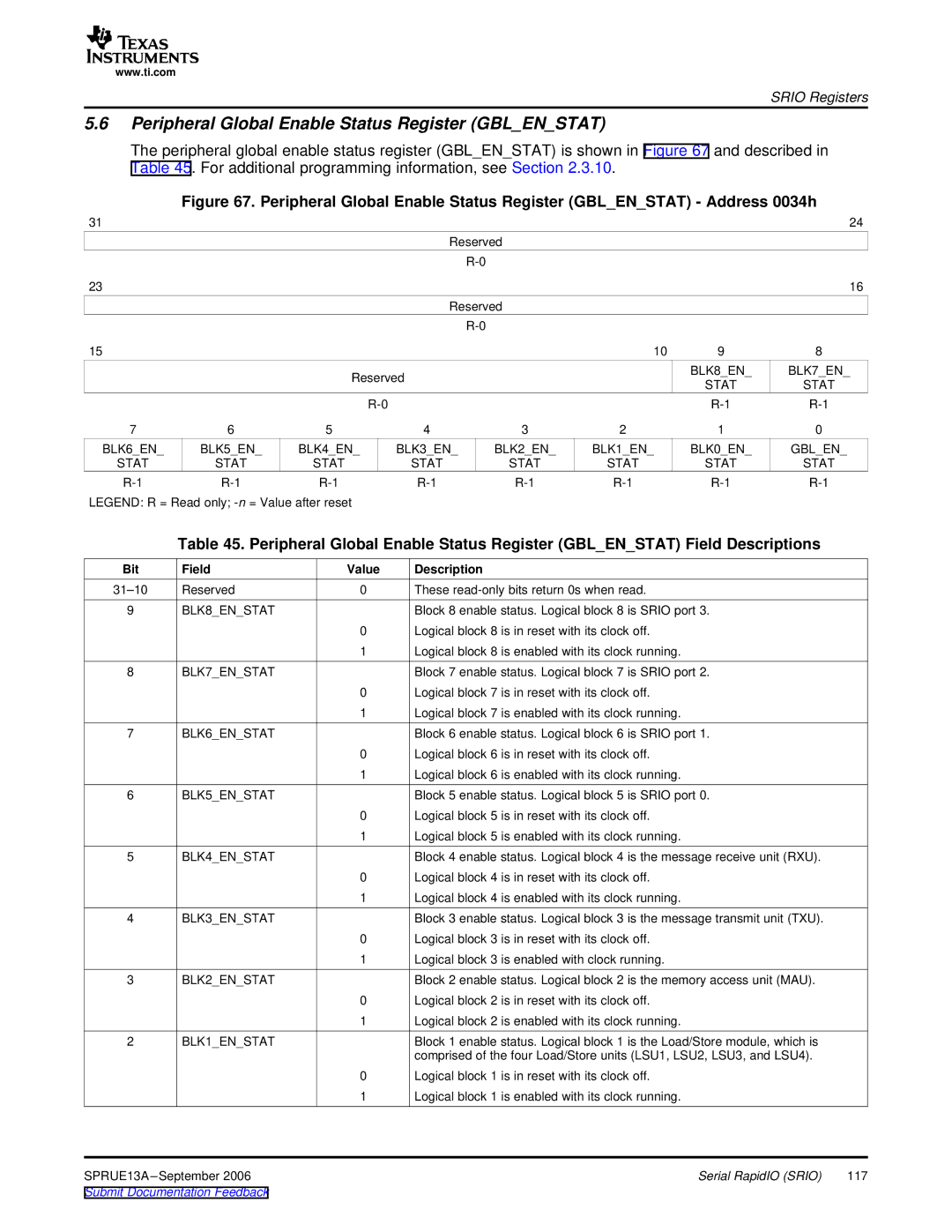

5.6Peripheral Global Enable Status Register (GBL_EN_STAT)

The peripheral global enable status register (GBL_EN_STAT) is shown in Figure 67 and described in Table 45. For additional programming information, see Section 2.3.10.

Figure 67. Peripheral Global Enable Status Register (GBL_EN_STAT) - Address 0034h

31 |

|

|

|

|

|

| 24 |

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

| |

23 |

|

|

|

|

|

| 16 |

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

| |

15 |

|

|

|

| 10 | 9 | 8 |

|

| Reserved |

|

| BLK8_EN_ | BLK7_EN_ | |

|

|

|

| STAT | STAT | ||

|

|

|

|

|

| ||

|

|

|

|

| |||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

BLK6_EN_ | BLK5_EN_ | BLK4_EN_ | BLK3_EN_ | BLK2_EN_ | BLK1_EN_ | BLK0_EN_ | GBL_EN_ |

STAT | STAT | STAT | STAT | STAT | STAT | STAT | STAT |

LEGEND: R = Read only;

Table 45. Peripheral Global Enable Status Register (GBL_EN_STAT) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | These | |

9 | BLK8_EN_STAT |

| Block 8 enable status. Logical block 8 is SRIO port 3. |

|

| 0 | Logical block 8 is in reset with its clock off. |

|

| 1 | Logical block 8 is enabled with its clock running. |

8 | BLK7_EN_STAT |

| Block 7 enable status. Logical block 7 is SRIO port 2. |

|

| 0 | Logical block 7 is in reset with its clock off. |

|

| 1 | Logical block 7 is enabled with its clock running. |

7 | BLK6_EN_STAT |

| Block 6 enable status. Logical block 6 is SRIO port 1. |

|

| 0 | Logical block 6 is in reset with its clock off. |

|

| 1 | Logical block 6 is enabled with its clock running. |

6 | BLK5_EN_STAT |

| Block 5 enable status. Logical block 5 is SRIO port 0. |

|

| 0 | Logical block 5 is in reset with its clock off. |

|

| 1 | Logical block 5 is enabled with its clock running. |

5 | BLK4_EN_STAT |

| Block 4 enable status. Logical block 4 is the message receive unit (RXU). |

|

| 0 | Logical block 4 is in reset with its clock off. |

|

| 1 | Logical block 4 is enabled with its clock running. |

4 | BLK3_EN_STAT |

| Block 3 enable status. Logical block 3 is the message transmit unit (TXU). |

|

| 0 | Logical block 3 is in reset with its clock off. |

|

| 1 | Logical block 3 is enabled with clock running. |

3 | BLK2_EN_STAT |

| Block 2 enable status. Logical block 2 is the memory access unit (MAU). |

|

| 0 | Logical block 2 is in reset with its clock off. |

|

| 1 | Logical block 2 is enabled with its clock running. |

2 | BLK1_EN_STAT |

| Block 1 enable status. Logical block 1 is the Load/Store module, which is |

|

|

| comprised of the four Load/Store units (LSU1, LSU2, LSU3, and LSU4). |

|

| 0 | Logical block 1 is in reset with its clock off. |

|

| 1 | Logical block 1 is enabled with its clock running. |

SPRUE13A | Serial RapidIO (SRIO) | 117 |

Submit Documentation Feedback |

|

|