www.ti.com

SRIO Registers

5.46 Transmit CPPI Supported Flow Mask Registers

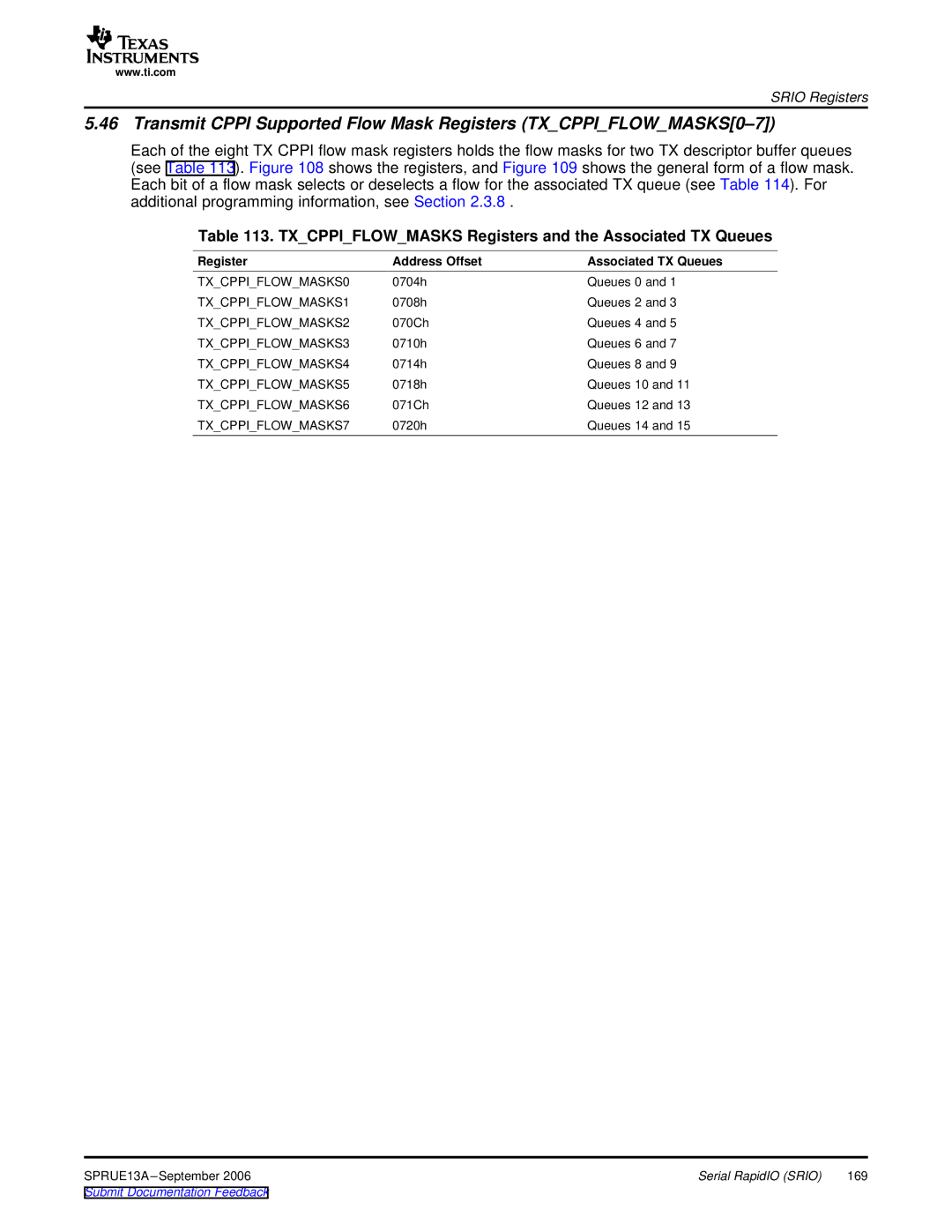

Each of the eight TX CPPI flow mask registers holds the flow masks for two TX descriptor buffer queues (see Table 113). Figure 108 shows the registers, and Figure 109 shows the general form of a flow mask. Each bit of a flow mask selects or deselects a flow for the associated TX queue (see Table 114). For additional programming information, see Section 2.3.8 .

Table 113. TX_CPPI_FLOW_MASKS Registers and the Associated TX Queues

Register | Address Offset | Associated TX Queues |

TX_CPPI_FLOW_MASKS0 | 0704h | Queues 0 and 1 |

TX_CPPI_FLOW_MASKS1 | 0708h | Queues 2 and 3 |

TX_CPPI_FLOW_MASKS2 | 070Ch | Queues 4 and 5 |

TX_CPPI_FLOW_MASKS3 | 0710h | Queues 6 and 7 |

TX_CPPI_FLOW_MASKS4 | 0714h | Queues 8 and 9 |

TX_CPPI_FLOW_MASKS5 | 0718h | Queues 10 and 11 |

TX_CPPI_FLOW_MASKS6 | 071Ch | Queues 12 and 13 |

TX_CPPI_FLOW_MASKS7 | 0720h | Queues 14 and 15 |

SPRUE13A | Serial RapidIO (SRIO) | 169 |

Submit Documentation Feedback |

|

|