www.ti.com

SRIO Functional Description

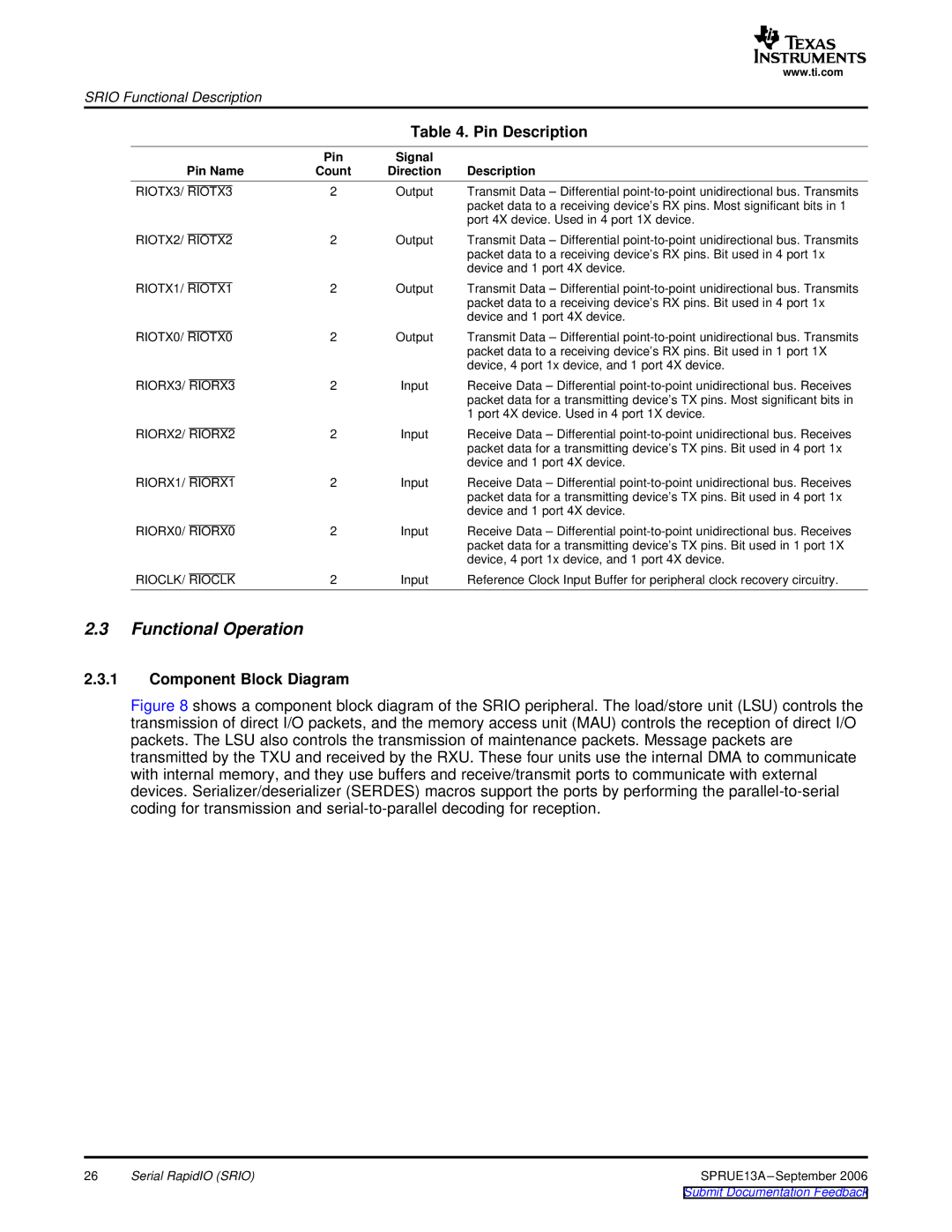

Table 4. Pin Description

| Pin | Signal |

|

Pin Name | Count | Direction | Description |

RIOTX3/ RIOTX3 | 2 | Output | Transmit Data – Differential |

|

|

| packet data to a receiving device’s RX pins. Most significant bits in 1 |

|

|

| port 4X device. Used in 4 port 1X device. |

RIOTX2/ RIOTX2 | 2 | Output | Transmit Data – Differential |

|

|

| packet data to a receiving device’s RX pins. Bit used in 4 port 1x |

|

|

| device and 1 port 4X device. |

RIOTX1/ RIOTX1 | 2 | Output | Transmit Data – Differential |

|

|

| packet data to a receiving device’s RX pins. Bit used in 4 port 1x |

|

|

| device and 1 port 4X device. |

RIOTX0/ RIOTX0 | 2 | Output | Transmit Data – Differential |

|

|

| packet data to a receiving device’s RX pins. Bit used in 1 port 1X |

|

|

| device, 4 port 1x device, and 1 port 4X device. |

RIORX3/ RIORX3 | 2 | Input | Receive Data – Differential |

|

|

| packet data for a transmitting device’s TX pins. Most significant bits in |

|

|

| 1 port 4X device. Used in 4 port 1X device. |

RIORX2/ RIORX2 | 2 | Input | Receive Data – Differential |

|

|

| packet data for a transmitting device’s TX pins. Bit used in 4 port 1x |

|

|

| device and 1 port 4X device. |

RIORX1/ RIORX1 | 2 | Input | Receive Data – Differential |

|

|

| packet data for a transmitting device’s TX pins. Bit used in 4 port 1x |

|

|

| device and 1 port 4X device. |

RIORX0/ RIORX0 | 2 | Input | Receive Data – Differential |

|

|

| packet data for a transmitting device’s TX pins. Bit used in 1 port 1X |

|

|

| device, 4 port 1x device, and 1 port 4X device. |

RIOCLK/ RIOCLK | 2 | Input | Reference Clock Input Buffer for peripheral clock recovery circuitry. |

2.3Functional Operation

2.3.1Component Block Diagram

Figure 8 shows a component block diagram of the SRIO peripheral. The load/store unit (LSU) controls the transmission of direct I/O packets, and the memory access unit (MAU) controls the reception of direct I/O packets. The LSU also controls the transmission of maintenance packets. Message packets are transmitted by the TXU and received by the RXU. These four units use the internal DMA to communicate with internal memory, and they use buffers and receive/transmit ports to communicate with external devices. Serializer/deserializer (SERDES) macros support the ports by performing the parallel-to-serial coding for transmission and serial-to-parallel decoding for reception.

26 | Serial RapidIO (SRIO) | SPRUE13A |