www.ti.com

SRIO Registers

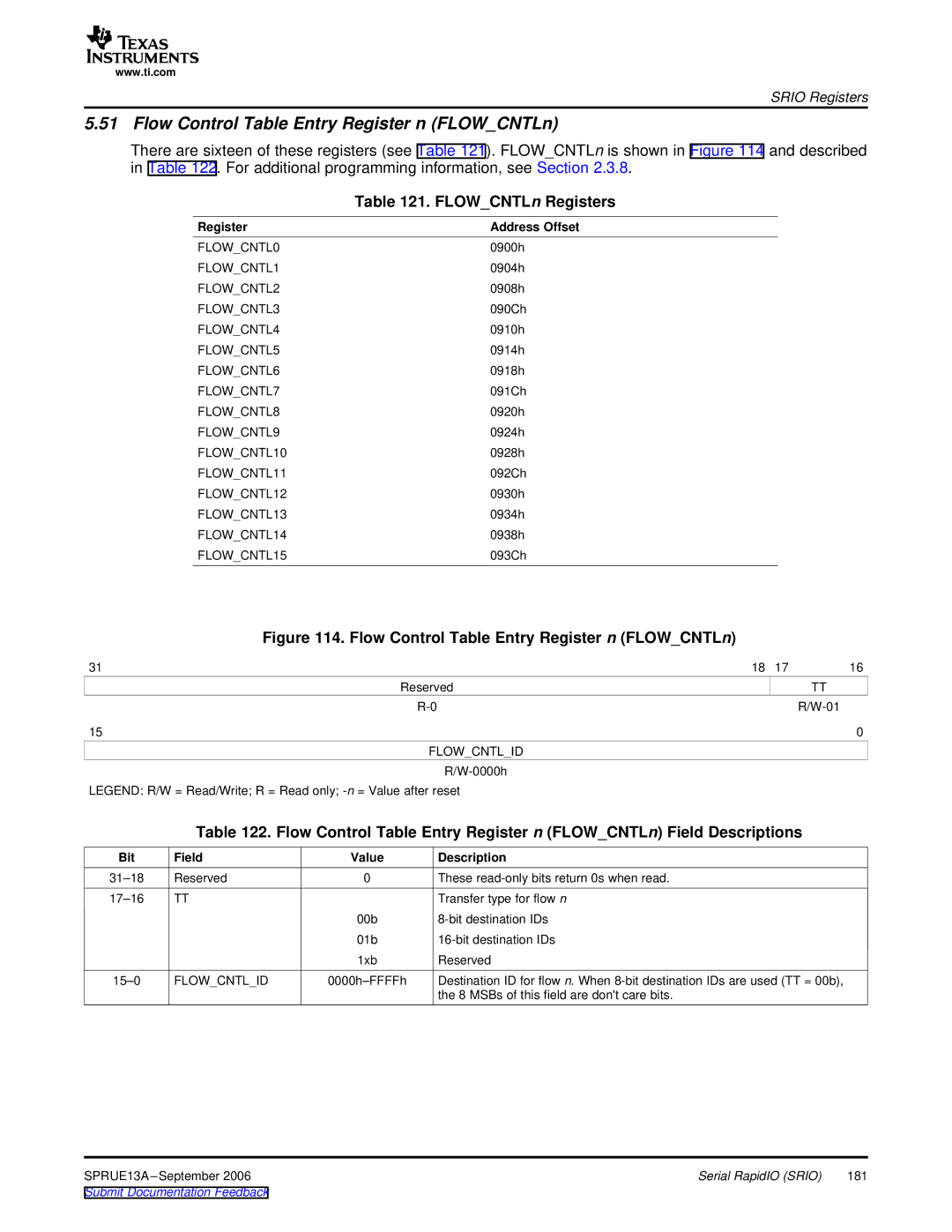

5.51 Flow Control Table Entry Register n (FLOW_CNTLn)

There are sixteen of these registers (see Table 121). FLOW_CNTLn is shown in Figure 114 and described in Table 122. For additional programming information, see Section 2.3.8.

| Table 121. FLOW_CNTLn Registers |

Register | Address Offset |

FLOW_CNTL0 | 0900h |

FLOW_CNTL1 | 0904h |

FLOW_CNTL2 | 0908h |

FLOW_CNTL3 | 090Ch |

FLOW_CNTL4 | 0910h |

FLOW_CNTL5 | 0914h |

FLOW_CNTL6 | 0918h |

FLOW_CNTL7 | 091Ch |

FLOW_CNTL8 | 0920h |

FLOW_CNTL9 | 0924h |

FLOW_CNTL10 | 0928h |

FLOW_CNTL11 | 092Ch |

FLOW_CNTL12 | 0930h |

FLOW_CNTL13 | 0934h |

FLOW_CNTL14 | 0938h |

FLOW_CNTL15 | 093Ch |

Figure 114. Flow Control Table Entry Register n (FLOW_CNTLn)

31 | 18 | 17 | 16 |

Reserved |

|

| TT |

|

| ||

15 |

|

| 0 |

FLOW_CNTL_ID |

|

|

|

|

|

| |

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

Table 122. Flow Control Table Entry Register n (FLOW_CNTLn) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | These | |

TT |

| Transfer type for flow n | |

|

| 00b | |

|

| 01b | |

|

| 1xb | Reserved |

FLOW_CNTL_ID | Destination ID for flow n. When | ||

|

|

| the 8 MSBs of this field are don'tcare bits. |

SPRUE13A | Serial RapidIO (SRIO) | 181 |

Submit Documentation Feedback |

|

|