www.ti.com

SRIO Registers

5.93 Port IP Prescaler Register (IP_PRESCAL)

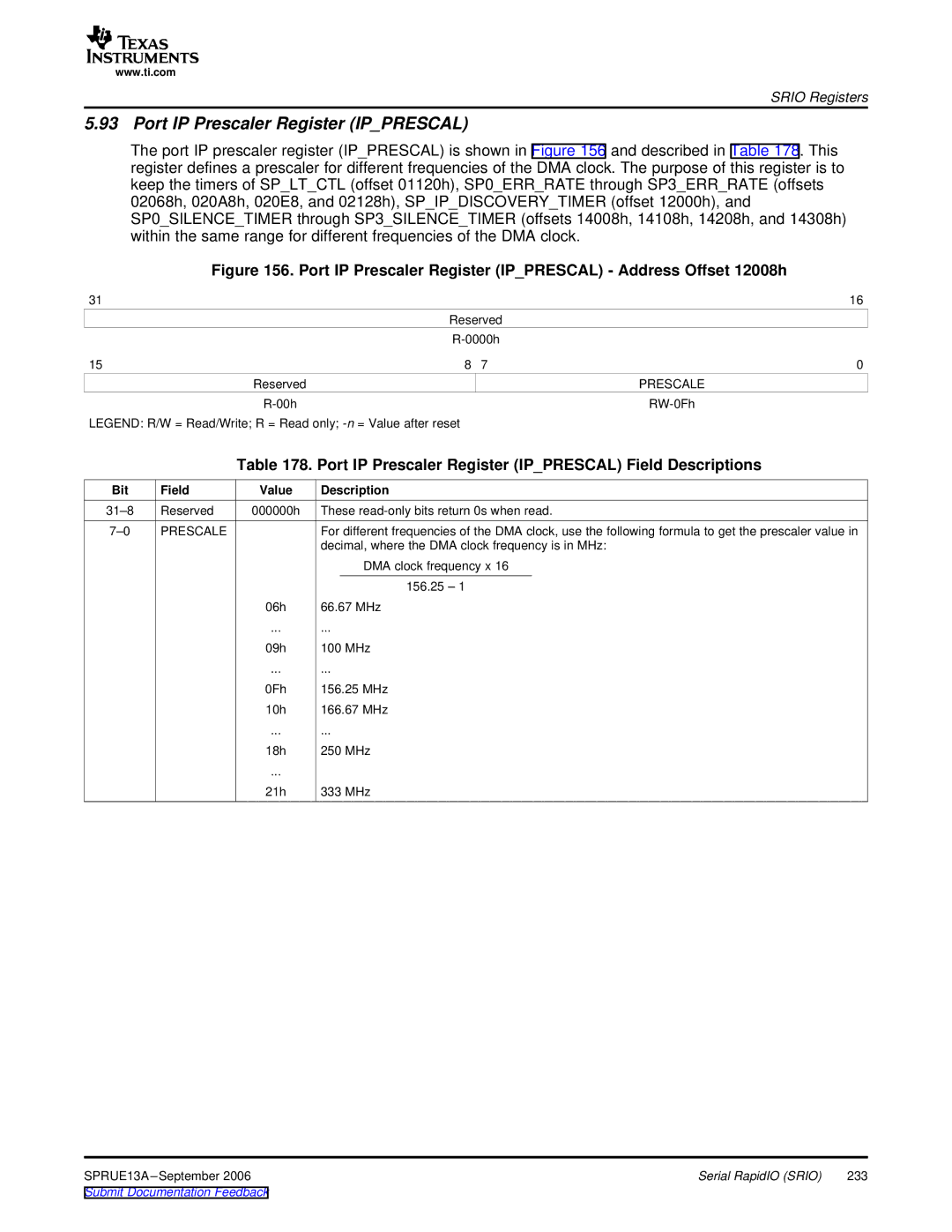

The port IP prescaler register (IP_PRESCAL) is shown in Figure 156 and described in Table 178. This register defines a prescaler for different frequencies of the DMA clock. The purpose of this register is to keep the timers of SP_LT_CTL (offset 01120h), SP0_ERR_RATE through SP3_ERR_RATE (offsets 02068h, 020A8h, 020E8, and 02128h), SP_IP_DISCOVERY_TIMER (offset 12000h), and SP0_SILENCE_TIMER through SP3_SILENCE_TIMER (offsets 14008h, 14108h, 14208h, and 14308h) within the same range for different frequencies of the DMA clock.

Figure 156. Port IP Prescaler Register (IP_PRESCAL) - Address Offset 12008h

31 |

|

| 16 |

| Reserved |

| |

|

| ||

15 | 8 | 7 | 0 |

Reserved |

|

| PRESCALE |

|

| ||

LEGEND: R/W = Read/Write; R = Read only;

Table 178. Port IP Prescaler Register (IP_PRESCAL) Field Descriptions

Bit | Field | Value | Description |

Reserved | 000000h | These | |

PRESCALE |

| For different frequencies of the DMA clock, use the following formula to get the prescaler value in | |

|

|

| decimal, where the DMA clock frequency is in MHz: |

|

|

| DMA clock frequency x 16 |

|

|

| 156.25 – 1 |

|

| 06h | 66.67 MHz |

|

| ... | ... |

|

| 09h | 100 MHz |

|

| ... | ... |

|

| 0Fh | 156.25 MHz |

|

| 10h | 166.67 MHz |

|

| ... | ... |

|

| 18h | 250 MHz |

|

| ... |

|

|

| 21h | 333 MHz |

SPRUE13A | Serial RapidIO (SRIO) | 233 |

Submit Documentation Feedback |

|

|