www.ti.com

SRIO Registers

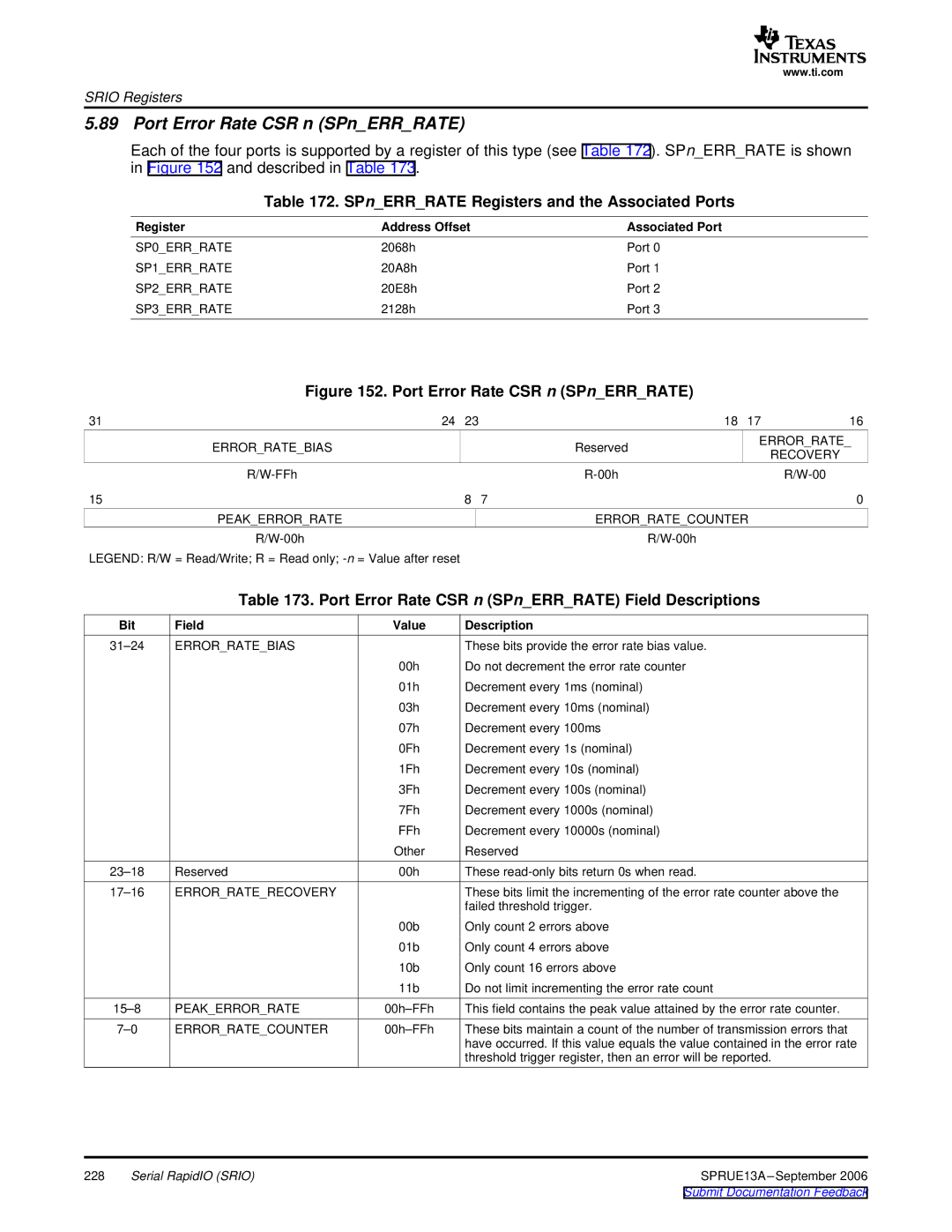

5.89 Port Error Rate CSR n (SPn_ERR_RATE)

Each of the four ports is supported by a register of this type (see Table 172). SPn_ERR_RATE is shown in Figure 152 and described in Table 173.

Table 172. SPn_ERR_RATE Registers and the Associated Ports

Register | Address Offset | Associated Port |

SP0_ERR_RATE | 2068h | Port 0 |

SP1_ERR_RATE | 20A8h | Port 1 |

SP2_ERR_RATE | 20E8h | Port 2 |

SP3_ERR_RATE | 2128h | Port 3 |

Figure 152. Port Error Rate CSR n (SPn_ERR_RATE)

31 | 24 | 23 |

| 18 | 17 | 16 |

| ERROR_RATE_BIAS |

|

| Reserved | ERROR_RATE_ | |

|

|

|

| RECOVERY | ||

|

|

|

|

|

| |

|

|

|

| |||

15 |

| 8 | 7 |

|

| 0 |

| PEAK_ERROR_RATE |

|

| ERROR_RATE_COUNTER |

| |

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

|

| |

Table 173. Port Error Rate CSR n (SPn_ERR_RATE) Field Descriptions

Bit | Field | Value | Description |

ERROR_RATE_BIAS |

| These bits provide the error rate bias value. | |

|

| 00h | Do not decrement the error rate counter |

|

| 01h | Decrement every 1ms (nominal) |

|

| 03h | Decrement every 10ms (nominal) |

|

| 07h | Decrement every 100ms |

|

| 0Fh | Decrement every 1s (nominal) |

|

| 1Fh | Decrement every 10s (nominal) |

|

| 3Fh | Decrement every 100s (nominal) |

|

| 7Fh | Decrement every 1000s (nominal) |

|

| FFh | Decrement every 10000s (nominal) |

|

| Other | Reserved |

Reserved | 00h | These | |

ERROR_RATE_RECOVERY |

| These bits limit the incrementing of the error rate counter above the | |

|

|

| failed threshold trigger. |

|

| 00b | Only count 2 errors above |

|

| 01b | Only count 4 errors above |

|

| 10b | Only count 16 errors above |

|

| 11b | Do not limit incrementing the error rate count |

PEAK_ERROR_RATE | This field contains the peak value attained by the error rate counter. | ||

ERROR_RATE_COUNTER | These bits maintain a count of the number of transmission errors that | ||

|

|

| have occurred. If this value equals the value contained in the error rate |

|

|

| threshold trigger register, then an error will be reported. |

228 | Serial RapidIO (SRIO) | SPRUE13A |