www.ti.com

SRIO Functional Description

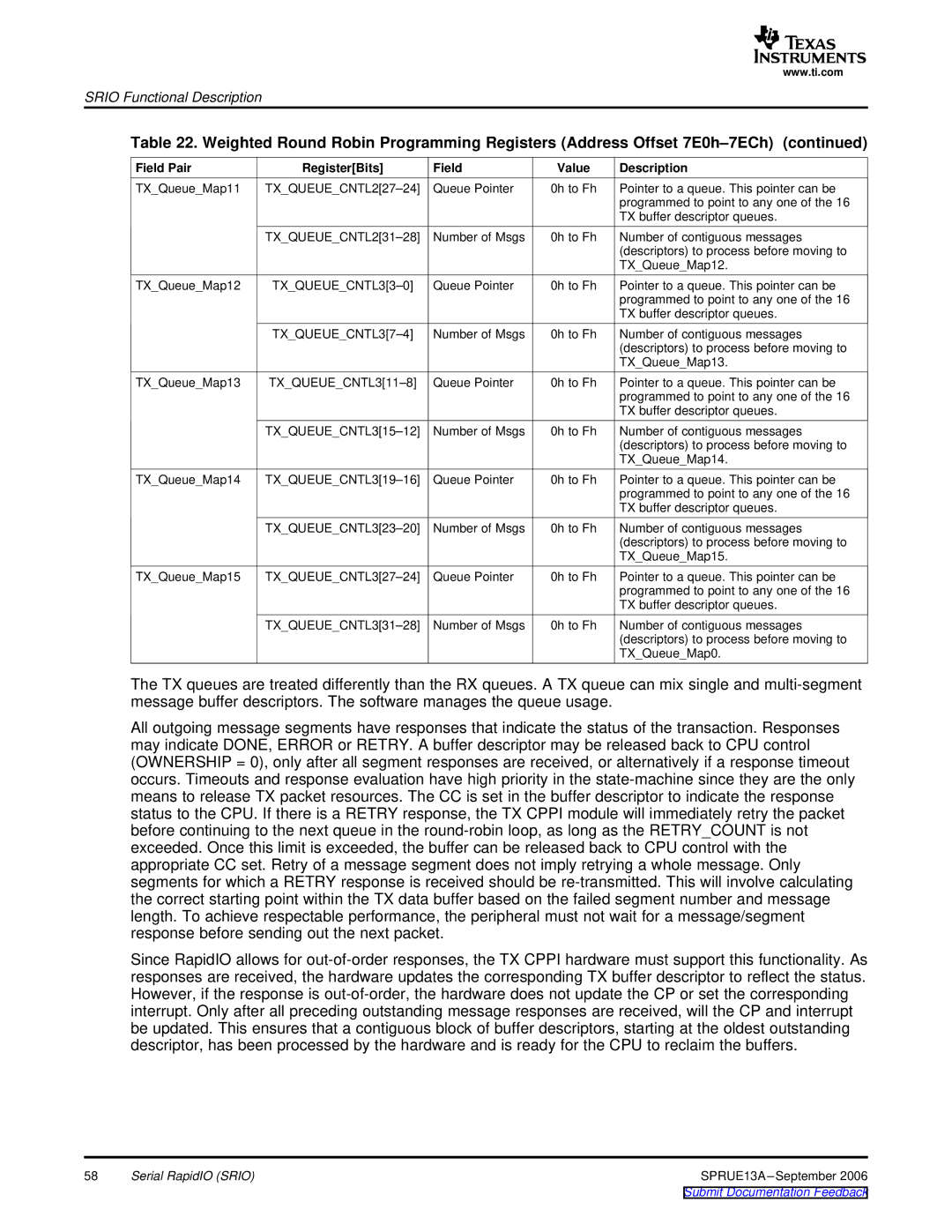

Table 22. Weighted Round Robin Programming Registers (Address Offset 7E0h–7ECh) (continued)

Field Pair | Register[Bits] | Field | Value | Description |

TX_Queue_Map11 | Queue Pointer | 0h to Fh | Pointer to a queue. This pointer can be | |

|

|

|

| programmed to point to any one of the 16 |

|

|

|

| TX buffer descriptor queues. |

| Number of Msgs | 0h to Fh | Number of contiguous messages | |

|

|

|

| (descriptors) to process before moving to |

|

|

|

| TX_Queue_Map12. |

TX_Queue_Map12 |

| Queue Pointer | 0h to Fh | Pointer to a queue. This pointer can be |

|

|

|

| programmed to point to any one of the 16 |

|

|

|

| TX buffer descriptor queues. |

|

| Number of Msgs | 0h to Fh | Number of contiguous messages |

|

|

|

| (descriptors) to process before moving to |

|

|

|

| TX_Queue_Map13. |

TX_Queue_Map13 |

| Queue Pointer | 0h to Fh | Pointer to a queue. This pointer can be |

|

|

|

| programmed to point to any one of the 16 |

|

|

|

| TX buffer descriptor queues. |

| Number of Msgs | 0h to Fh | Number of contiguous messages | |

|

|

|

| (descriptors) to process before moving to |

|

|

|

| TX_Queue_Map14. |

TX_Queue_Map14 | Queue Pointer | 0h to Fh | Pointer to a queue. This pointer can be | |

|

|

|

| programmed to point to any one of the 16 |

|

|

|

| TX buffer descriptor queues. |

| Number of Msgs | 0h to Fh | Number of contiguous messages | |

|

|

|

| (descriptors) to process before moving to |

|

|

|

| TX_Queue_Map15. |

TX_Queue_Map15 | Queue Pointer | 0h to Fh | Pointer to a queue. This pointer can be | |

|

|

|

| programmed to point to any one of the 16 |

|

|

|

| TX buffer descriptor queues. |

| Number of Msgs | 0h to Fh | Number of contiguous messages | |

|

|

|

| (descriptors) to process before moving to |

|

|

|

| TX_Queue_Map0. |

The TX queues are treated differently than the RX queues. A TX queue can mix single and

All outgoing message segments have responses that indicate the status of the transaction. Responses may indicate DONE, ERROR or RETRY. A buffer descriptor may be released back to CPU control (OWNERSHIP = 0), only after all segment responses are received, or alternatively if a response timeout occurs. Timeouts and response evaluation have high priority in the

Since RapidIO allows for

58 | Serial RapidIO (SRIO) | SPRUE13A |