www.ti.com

SRIO Functional Description

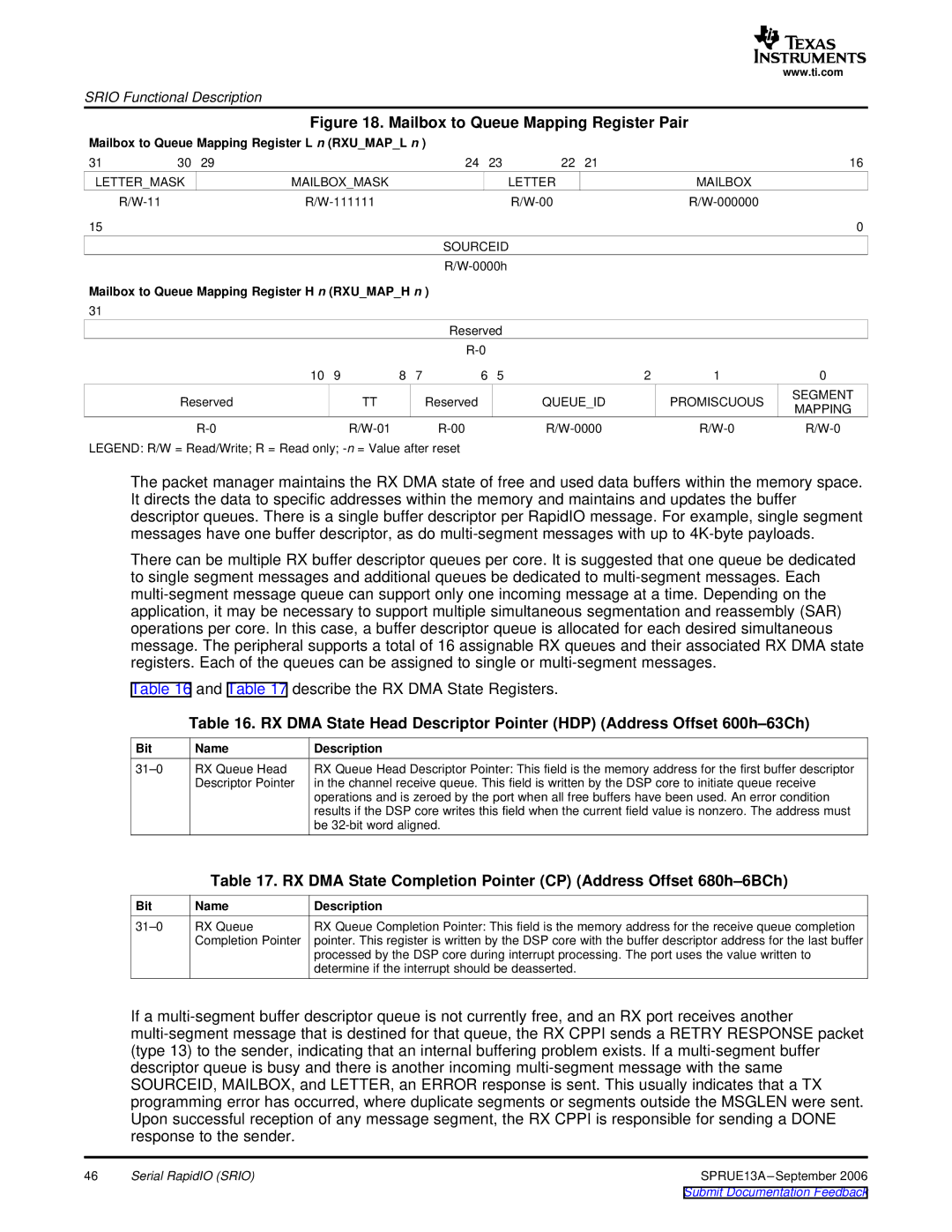

Figure 18. Mailbox to Queue Mapping Register Pair

Mailbox to Queue Mapping Register L n (RXU_MAP_L n )

31 | 30 | 29 | 24 | 23 | 22 | 21 | 16 |

LETTER_MASK | MAILBOX_MASK |

| LETTER |

|

| MAILBOX | |

|

|

|

| ||||

15 |

|

|

|

|

|

| 0 |

|

|

| SOURCEID |

|

|

| |

|

|

|

|

|

| ||

Mailbox to Queue Mapping Register H n (RXU_MAP_H n )

31

Reserved

10 | 9 | 8 | 7 | 6 | 5 | 2 | 1 | 0 |

Reserved |

| TT | Reserved |

| QUEUE_ID |

| PROMISCUOUS | SEGMENT |

|

|

| MAPPING | |||||

|

|

|

|

|

|

|

| |

|

|

|

LEGEND: R/W = Read/Write; R = Read only;

The packet manager maintains the RX DMA state of free and used data buffers within the memory space. It directs the data to specific addresses within the memory and maintains and updates the buffer descriptor queues. There is a single buffer descriptor per RapidIO message. For example, single segment messages have one buffer descriptor, as do

There can be multiple RX buffer descriptor queues per core. It is suggested that one queue be dedicated to single segment messages and additional queues be dedicated to

Table 16 and Table 17 describe the RX DMA State Registers.

Table 16. RX DMA State Head Descriptor Pointer (HDP) (Address Offset

Bit | Name | Description |

| RX Queue Head | RX Queue Head Descriptor Pointer: This field is the memory address for the first buffer descriptor |

| Descriptor Pointer | in the channel receive queue. This field is written by the DSP core to initiate queue receive |

|

| operations and is zeroed by the port when all free buffers have been used. An error condition |

|

| results if the DSP core writes this field when the current field value is nonzero. The address must |

|

| be |

Table 17. RX DMA State Completion Pointer (CP) (Address Offset 680h–6BCh)

Bit | Name | Description |

RX Queue | RX Queue Completion Pointer: This field is the memory address for the receive queue completion | |

| Completion Pointer | pointer. This register is written by the DSP core with the buffer descriptor address for the last buffer |

|

| processed by the DSP core during interrupt processing. The port uses the value written to |

|

| determine if the interrupt should be deasserted. |

If a

46 | Serial RapidIO (SRIO) | SPRUE13A |