www.ti.com

|

|

|

|

|

|

| Interrupt Conditions |

|

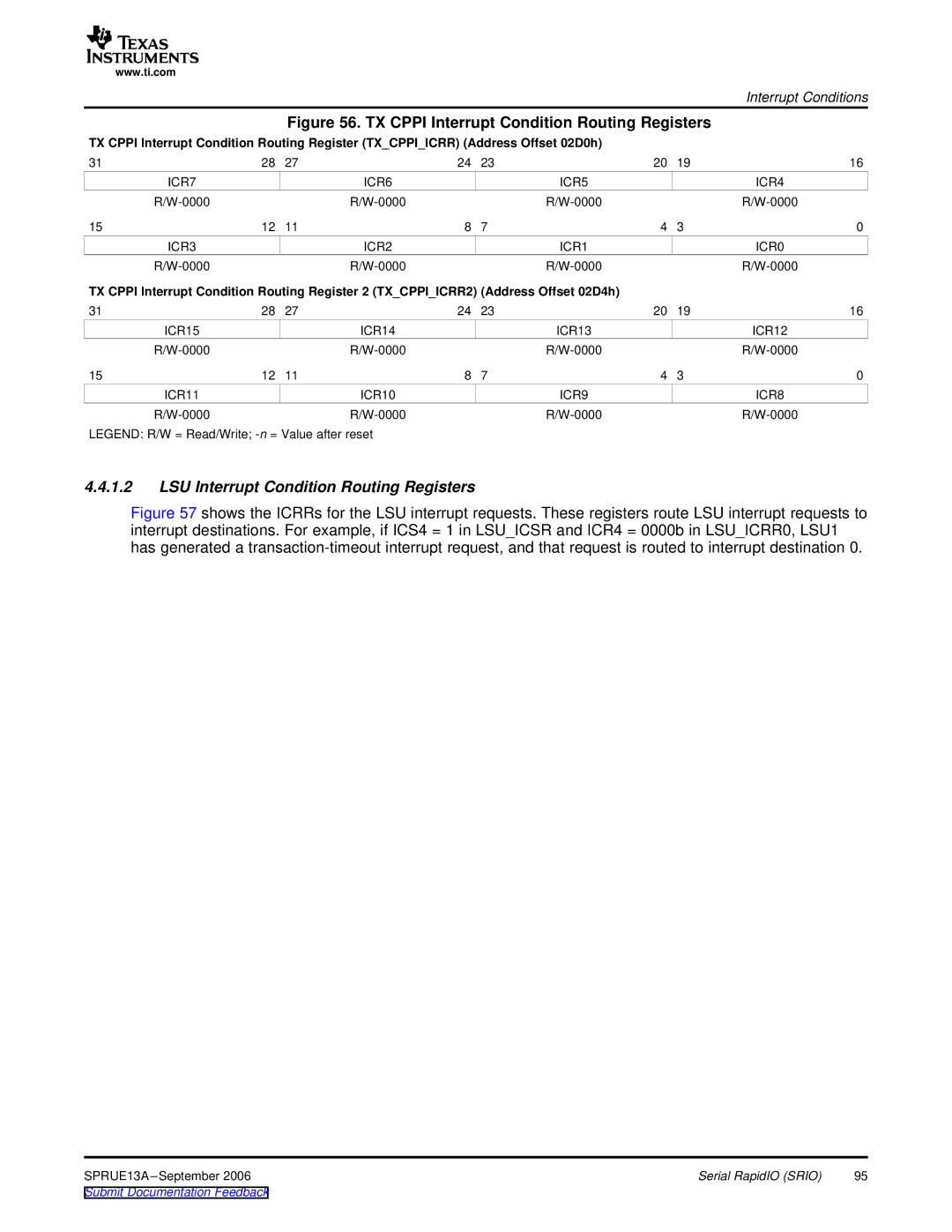

| Figure 56. TX CPPI Interrupt Condition Routing Registers |

| ||||

TX CPPI Interrupt Condition Routing Register (TX_CPPI_ICRR) (Address Offset 02D0h) |

|

| |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 | 16 |

ICR7 |

|

| ICR6 |

| ICR5 |

| ICR4 |

|

|

|

| ||||

15 | 12 | 11 | 8 | 7 | 4 | 3 | 0 |

ICR3 |

|

| ICR2 |

| ICR1 |

| ICR0 |

|

|

|

| ||||

TX CPPI Interrupt Condition Routing Register 2 (TX_CPPI_ICRR2) (Address Offset 02D4h) |

|

| |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 | 16 |

ICR15 |

|

| ICR14 |

| ICR13 |

| ICR12 |

|

|

|

| ||||

15 | 12 | 11 | 8 | 7 | 4 | 3 | 0 |

ICR11 |

|

| ICR10 |

| ICR9 |

| ICR8 |

|

|

|

| ||||

LEGEND: R/W = Read/Write;

4.4.1.2LSU Interrupt Condition Routing Registers

Figure 57 shows the ICRRs for the LSU interrupt requests. These registers route LSU interrupt requests to interrupt destinations. For example, if ICS4 = 1 in LSU_ICSR and ICR4 = 0000b in LSU_ICRR0, LSU1 has generated a transaction-timeout interrupt request, and that request is routed to interrupt destination 0.

SPRUE13A | Serial RapidIO (SRIO) | 95 |