www.ti.com

SRIO Registers

5.41 Queue n Transmit DMA Head Descriptor Pointer Register (QUEUEn_TXDMA_HDP)

There are sixteen of these registers (see Table 104). QUEUEn_TXDMA_HDP is shown in Figure 103 and described in Table 105. For additional programming information, see Section 2.3.4.2 .

Table 104. QUEUEn_TXDMA_HDP Registers

Register | Address Offset |

QUEUE0_TXDMA_HDP | 0500h |

QUEUE1_TXDMA_HDP | 0504h |

QUEUE2_TXDMA_HDP | 0508h |

QUEUE3_TXDMA_HDP | 050Ch |

QUEUE4_TXDMA_HDP | 0510h |

QUEUE5_TXDMA_HDP | 0514h |

QUEUE6_TXDMA_HDP | 0518h |

QUEUE7_TXDMA_HDP | 051Ch |

QUEUE8_TXDMA_HDP | 0520h |

QUEUE9_TXDMA_HDP | 0524h |

QUEUE10_TXDMA_HDP | 0528h |

QUEUE11_TXDMA_HDP | 052Ch |

QUEUE12_TXDMA_HDP | 0530h |

QUEUE13_TXDMA_HDP | 0534h |

QUEUE14_TXDMA_HDP | 0538h |

QUEUE15_TXDMA_HDP | 053Ch |

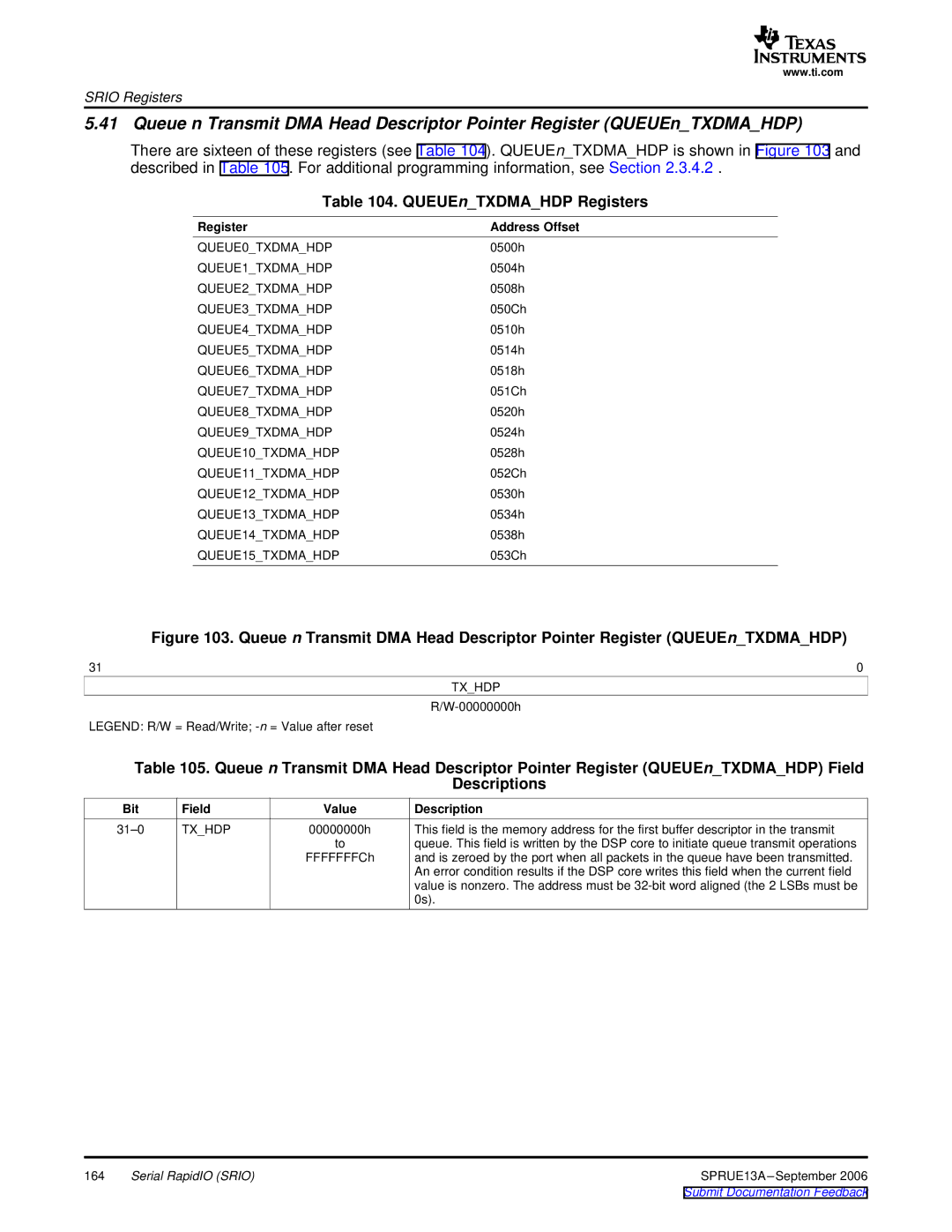

Figure 103. Queue n Transmit DMA Head Descriptor Pointer Register (QUEUEn_TXDMA_HDP)

31 | 0 |

TX_HDP

LEGEND: R/W = Read/Write;

Table 105. Queue n Transmit DMA Head Descriptor Pointer Register (QUEUEn_TXDMA_HDP) Field

Descriptions

Bit | Field | Value | Description |

TX_HDP | 00000000h | This field is the memory address for the first buffer descriptor in the transmit | |

|

| to | queue. This field is written by the DSP core to initiate queue transmit operations |

|

| FFFFFFFCh | and is zeroed by the port when all packets in the queue have been transmitted. |

|

|

| An error condition results if the DSP core writes this field when the current field |

|

|

| value is nonzero. The address must be |

|

|

| 0s). |

164 | Serial RapidIO (SRIO) | SPRUE13A |