www.ti.com

SRIO Registers

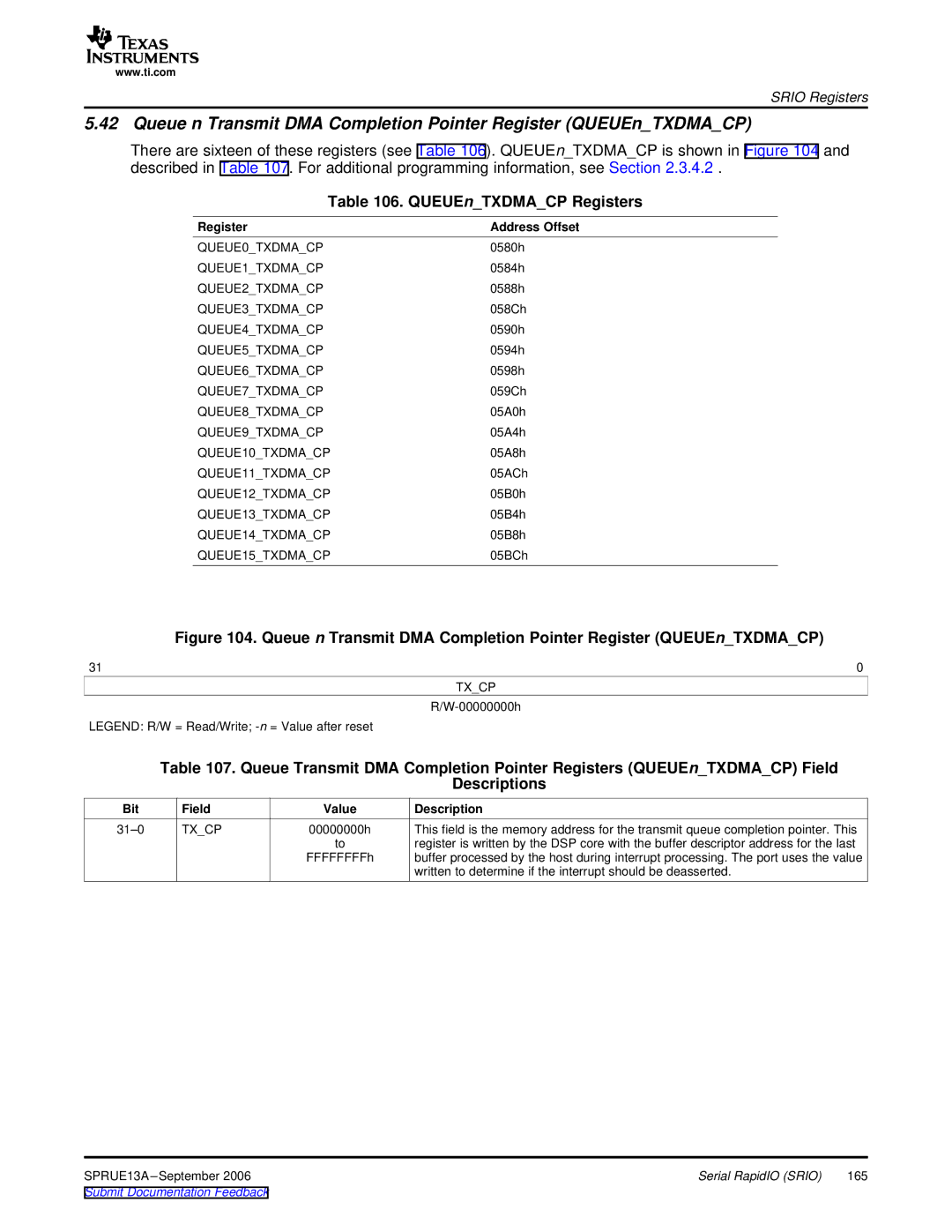

5.42 Queue n Transmit DMA Completion Pointer Register (QUEUEn_TXDMA_CP)

There are sixteen of these registers (see Table 106). QUEUEn_TXDMA_CP is shown in Figure 104 and described in Table 107. For additional programming information, see Section 2.3.4.2 .

Table 106. QUEUEn_TXDMA_CP Registers

Register | Address Offset |

QUEUE0_TXDMA_CP | 0580h |

QUEUE1_TXDMA_CP | 0584h |

QUEUE2_TXDMA_CP | 0588h |

QUEUE3_TXDMA_CP | 058Ch |

QUEUE4_TXDMA_CP | 0590h |

QUEUE5_TXDMA_CP | 0594h |

QUEUE6_TXDMA_CP | 0598h |

QUEUE7_TXDMA_CP | 059Ch |

QUEUE8_TXDMA_CP | 05A0h |

QUEUE9_TXDMA_CP | 05A4h |

QUEUE10_TXDMA_CP | 05A8h |

QUEUE11_TXDMA_CP | 05ACh |

QUEUE12_TXDMA_CP | 05B0h |

QUEUE13_TXDMA_CP | 05B4h |

QUEUE14_TXDMA_CP | 05B8h |

QUEUE15_TXDMA_CP | 05BCh |

Figure 104. Queue n Transmit DMA Completion Pointer Register (QUEUEn_TXDMA_CP)

31 | 0 |

TX_CP

LEGEND: R/W = Read/Write;

Table 107. Queue Transmit DMA Completion Pointer Registers (QUEUEn_TXDMA_CP) Field

Descriptions

Bit | Field | Value | Description |

TX_CP | 00000000h | This field is the memory address for the transmit queue completion pointer. This | |

|

| to | register is written by the DSP core with the buffer descriptor address for the last |

|

| FFFFFFFFh | buffer processed by the host during interrupt processing. The port uses the value |

|

|

| written to determine if the interrupt should be deasserted. |

SPRUE13A | Serial RapidIO (SRIO) | 165 |

Submit Documentation Feedback |

|

|