www.ti.com

SRIO Functional Description

2.3.10Reset and Power Down

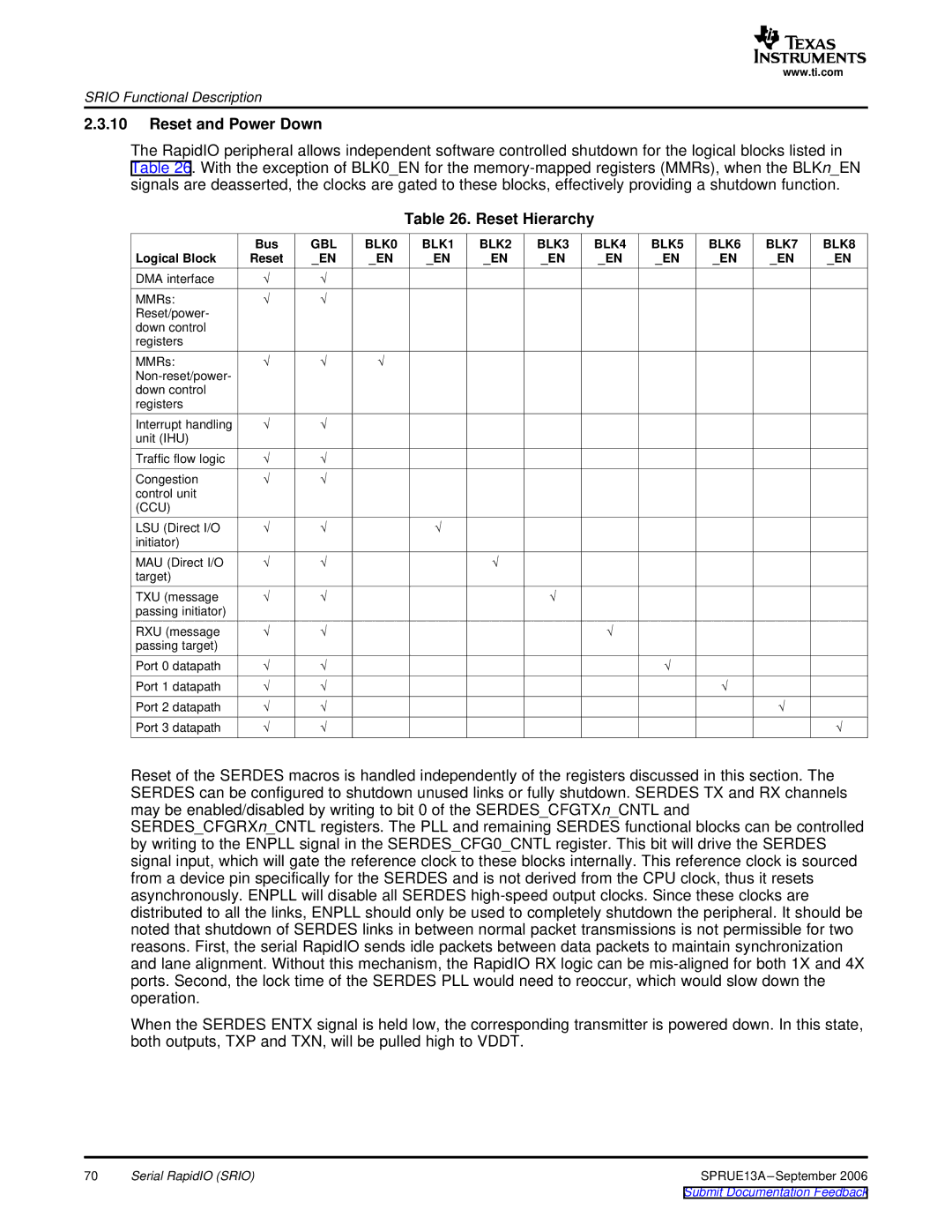

The RapidIO peripheral allows independent software controlled shutdown for the logical blocks listed in Table 26. With the exception of BLK0_EN for the

Table 26. Reset Hierarchy

| Bus | GBL | BLK0 | BLK1 | BLK2 | BLK3 | BLK4 | BLK5 | BLK6 | BLK7 | BLK8 |

Logical Block | Reset | _EN | _EN | _EN | _EN | _EN | _EN | _EN | _EN | _EN | _EN |

DMA interface | √ | √ |

|

|

|

|

|

|

|

|

|

MMRs: | √ | √ |

|

|

|

|

|

|

|

|

|

Reset/power- |

|

|

|

|

|

|

|

|

|

|

|

down control |

|

|

|

|

|

|

|

|

|

|

|

registers |

|

|

|

|

|

|

|

|

|

|

|

MMRs: | √ | √ | √ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

down control |

|

|

|

|

|

|

|

|

|

|

|

registers |

|

|

|

|

|

|

|

|

|

|

|

Interrupt handling | √ | √ |

|

|

|

|

|

|

|

|

|

unit (IHU) |

|

|

|

|

|

|

|

|

|

|

|

Traffic flow logic | √ | √ |

|

|

|

|

|

|

|

|

|

Congestion | √ | √ |

|

|

|

|

|

|

|

|

|

control unit |

|

|

|

|

|

|

|

|

|

|

|

(CCU) |

|

|

|

|

|

|

|

|

|

|

|

LSU (Direct I/O | √ | √ |

| √ |

|

|

|

|

|

|

|

initiator) |

|

|

|

|

|

|

|

|

|

|

|

MAU (Direct I/O | √ | √ |

|

| √ |

|

|

|

|

|

|

target) |

|

|

|

|

|

|

|

|

|

|

|

TXU (message | √ | √ |

|

|

| √ |

|

|

|

|

|

passing initiator) |

|

|

|

|

|

|

|

|

|

|

|

RXU (message | √ | √ |

|

|

|

| √ |

|

|

|

|

passing target) |

|

|

|

|

|

|

|

|

|

|

|

Port 0 datapath | √ | √ |

|

|

|

|

| √ |

|

|

|

Port 1 datapath | √ | √ |

|

|

|

|

|

| √ |

|

|

Port 2 datapath | √ | √ |

|

|

|

|

|

|

| √ |

|

Port 3 datapath | √ | √ |

|

|

|

|

|

|

|

| √ |

Reset of the SERDES macros is handled independently of the registers discussed in this section. The SERDES can be configured to shutdown unused links or fully shutdown. SERDES TX and RX channels may be enabled/disabled by writing to bit 0 of the SERDES_CFGTXn_CNTL and SERDES_CFGRXn_CNTL registers. The PLL and remaining SERDES functional blocks can be controlled by writing to the ENPLL signal in the SERDES_CFG0_CNTL register. This bit will drive the SERDES signal input, which will gate the reference clock to these blocks internally. This reference clock is sourced from a device pin specifically for the SERDES and is not derived from the CPU clock, thus it resets asynchronously. ENPLL will disable all SERDES

When the SERDES ENTX signal is held low, the corresponding transmitter is powered down. In this state, both outputs, TXP and TXN, will be pulled high to VDDT.

70 | Serial RapidIO (SRIO) | SPRUE13A |