www.ti.com

SRIO Functional Description

For

2.3.13Initialization Example

2.3.13.1Enabling the SRIO Peripheral

When the device is powered on, the SRIO peripheral is in a disabled state. Before any SRIO specific initialization can take place, the peripheral needs to be enabled; otherwise, its registers cannot be written, and the reads will all return a value of zero.

/* Glb enable srio */

SRIO_REGS->GBL_EN = 0x00000001 ;

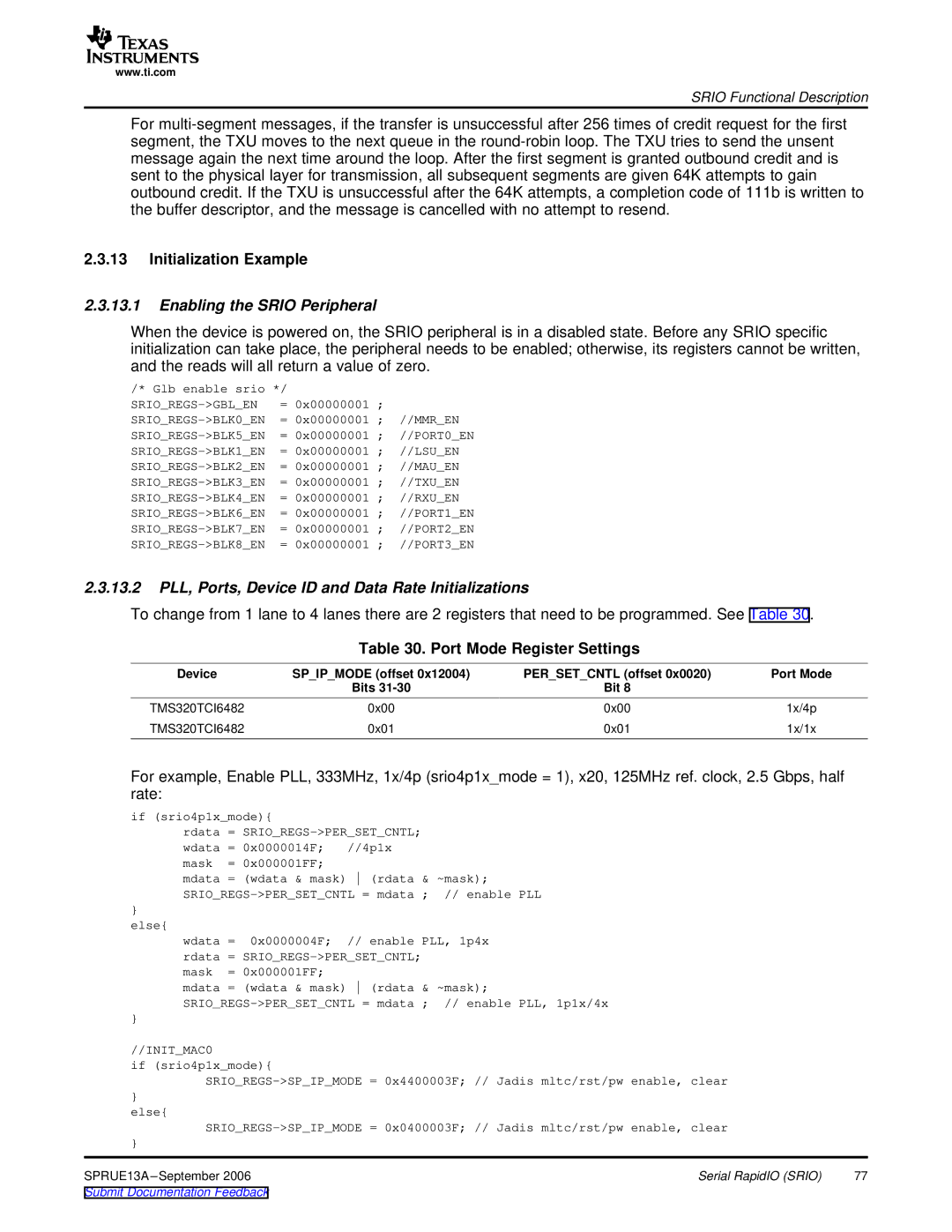

2.3.13.2PLL, Ports, Device ID and Data Rate Initializations

To change from 1 lane to 4 lanes there are 2 registers that need to be programmed. See Table 30.

Table 30. Port Mode Register Settings

Device | SP_IP_MODE (offset 0x12004) | PER_SET_CNTL (offset 0x0020) | Port Mode |

| Bits | Bit 8 |

|

TMS320TCI6482 | 0x00 | 0x00 | 1x/4p |

TMS320TCI6482 | 0x01 | 0x01 | 1x/1x |

For example, Enable PLL, 333MHz, 1x/4p (srio4p1x_mode = 1), x20, 125MHz ref. clock, 2.5 Gbps, half rate:

if (srio4p1x_mode){ |

|

|

| ||

rdata = |

|

|

| ||

wdata = | 0x0000014F; | //4p1x |

|

| |

mask | = | 0x000001FF; |

|

|

|

mdata = | (wdata & mask) (rdata & ~mask); |

| |||

// enable PLL |

| ||||

} |

|

|

|

|

|

else{ |

|

|

|

|

|

wdata = | 0x0000004F; | // enable PLL, 1p4x |

| ||

rdata = |

|

| |||

mask | = | 0x000001FF; |

|

|

|

mdata = | (wdata & mask) (rdata & ~mask); |

| |||

// enable PLL, 1p1x/4x |

| ||||

} |

|

|

|

|

|

//INIT_MAC0 |

|

|

|

|

|

if (srio4p1x_mode){ |

|

|

| ||

| |||||

} |

|

|

|

|

|

else{ |

|

|

|

|

|

| |||||

} |

|

|

|

|

|

SPRUE13A |

| Serial RapidIO (SRIO) | 77 | ||