www.ti.com

SRIO Registers

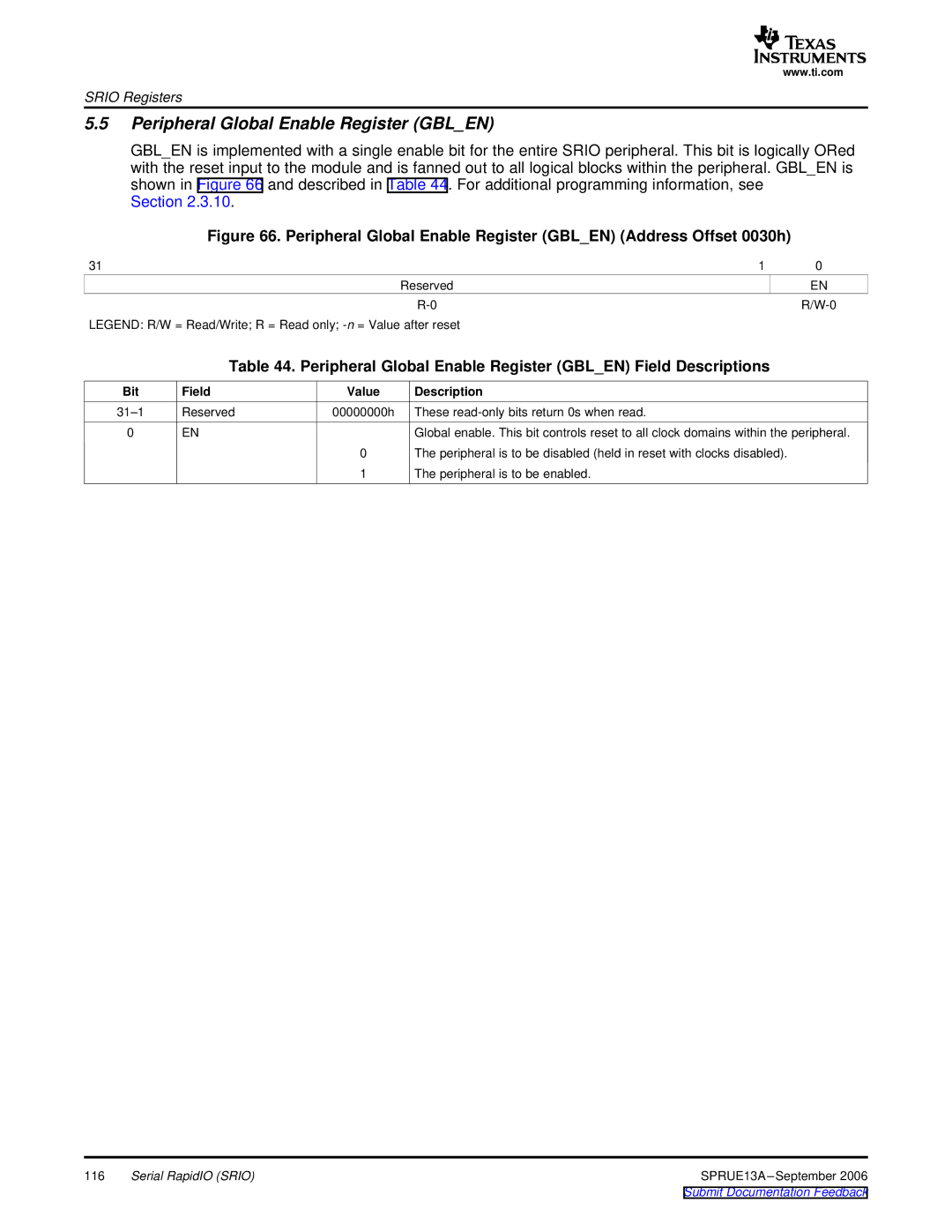

5.5Peripheral Global Enable Register (GBL_EN)

GBL_EN is implemented with a single enable bit for the entire SRIO peripheral. This bit is logically ORed with the reset input to the module and is fanned out to all logical blocks within the peripheral. GBL_EN is shown in Figure 66 and described in Table 44. For additional programming information, see

Section 2.3.10.

Figure 66. Peripheral Global Enable Register (GBL_EN) (Address Offset 0030h)

31 | 1 | 0 |

Reserved |

| EN |

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

Table 44. Peripheral Global Enable Register (GBL_EN) Field Descriptions

Bit | Field | Value | Description |

Reserved | 00000000h | These | |

0 | EN |

| Global enable. This bit controls reset to all clock domains within the peripheral. |

|

| 0 | The peripheral is to be disabled (held in reset with clocks disabled). |

|

| 1 | The peripheral is to be enabled. |

116 | Serial RapidIO (SRIO) | SPRUE13A |

|

| Submit Documentation Feedback |