www.ti.com

SRIO Functional Description

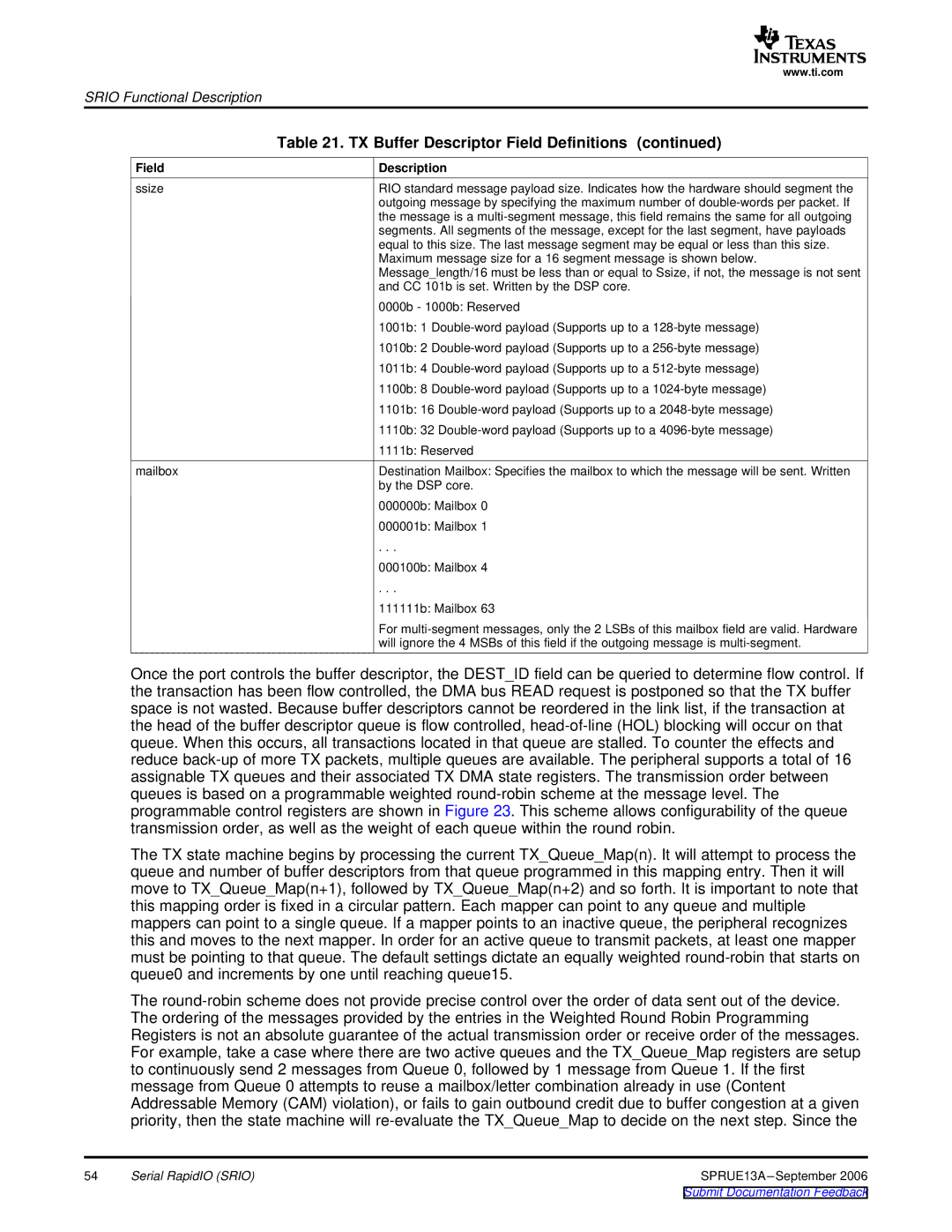

| Table 21. TX Buffer Descriptor Field Definitions (continued) |

Field | Description |

ssize | RIO standard message payload size. Indicates how the hardware should segment the |

| outgoing message by specifying the maximum number of |

| the message is a |

| segments. All segments of the message, except for the last segment, have payloads |

| equal to this size. The last message segment may be equal or less than this size. |

| Maximum message size for a 16 segment message is shown below. |

| Message_length/16 must be less than or equal to Ssize, if not, the message is not sent |

| and CC 101b is set. Written by the DSP core. |

| 0000b - 1000b: Reserved |

| 1001b: 1 |

| 1010b: 2 |

| 1011b: 4 |

| 1100b: 8 |

| 1101b: 16 |

| 1110b: 32 |

| 1111b: Reserved |

mailbox | Destination Mailbox: Specifies the mailbox to which the message will be sent. Written |

| by the DSP core. |

| 000000b: Mailbox 0 |

| 000001b: Mailbox 1 |

| . . . |

| 000100b: Mailbox 4 |

| . . . |

| 111111b: Mailbox 63 |

| For |

| will ignore the 4 MSBs of this field if the outgoing message is |

Once the port controls the buffer descriptor, the DEST_ID field can be queried to determine flow control. If the transaction has been flow controlled, the DMA bus READ request is postponed so that the TX buffer space is not wasted. Because buffer descriptors cannot be reordered in the link list, if the transaction at the head of the buffer descriptor queue is flow controlled,

The TX state machine begins by processing the current TX_Queue_Map(n). It will attempt to process the queue and number of buffer descriptors from that queue programmed in this mapping entry. Then it will move to TX_Queue_Map(n+1), followed by TX_Queue_Map(n+2) and so forth. It is important to note that this mapping order is fixed in a circular pattern. Each mapper can point to any queue and multiple mappers can point to a single queue. If a mapper points to an inactive queue, the peripheral recognizes this and moves to the next mapper. In order for an active queue to transmit packets, at least one mapper must be pointing to that queue. The default settings dictate an equally weighted

The

54 | Serial RapidIO (SRIO) | SPRUE13A |