www.ti.com

SRIO Registers

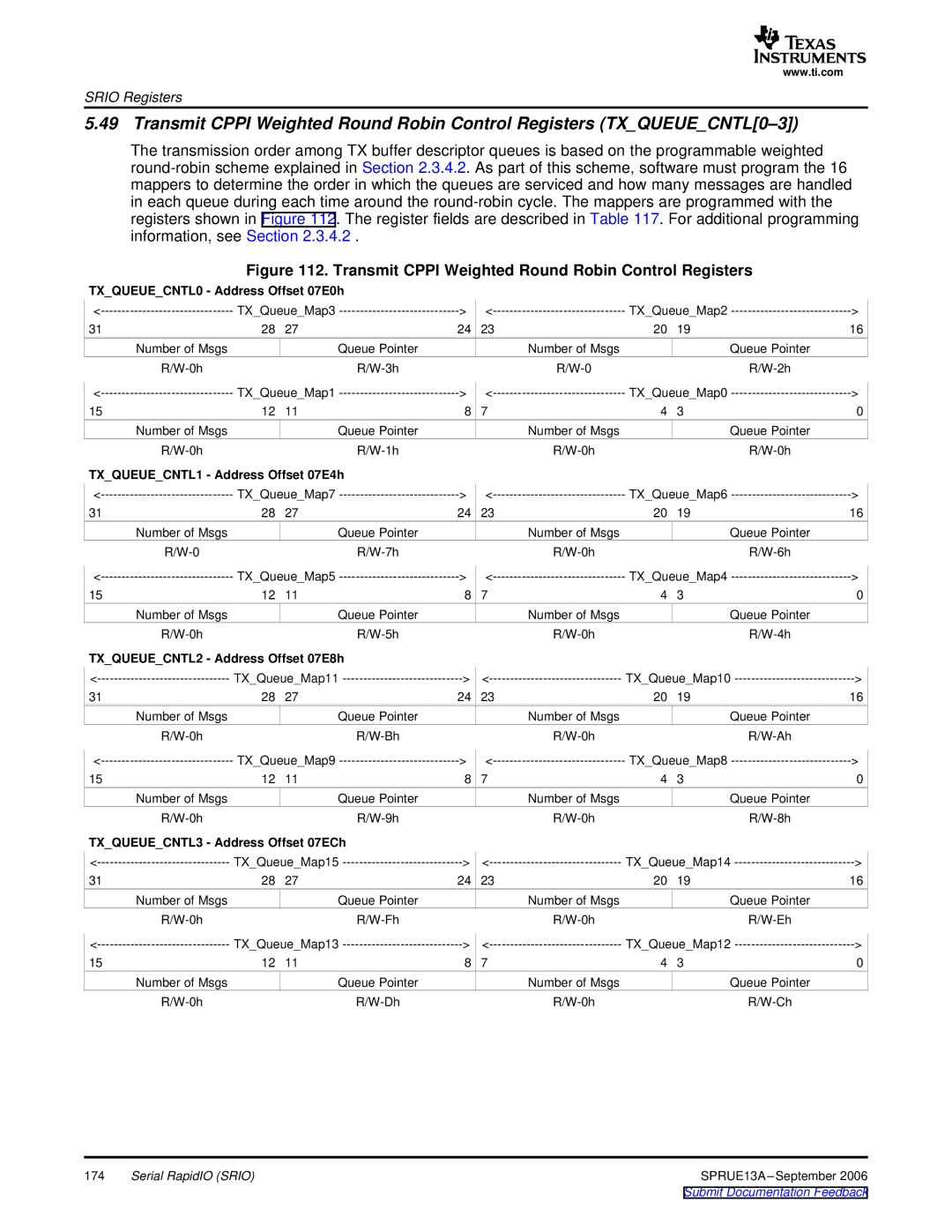

5.49 Transmit CPPI Weighted Round Robin Control Registers

The transmission order among TX buffer descriptor queues is based on the programmable weighted

Figure 112. Transmit CPPI Weighted Round Robin Control Registers

TX_QUEUE_CNTL0 - Address Offset 07E0h |

|

|

|

|

|

| ||

TX_Queue_Map3 | > | TX_Queue_Map2 | > | |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 |

| 16 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_Queue_Map1 | > | TX_Queue_Map0 | > | |||||

15 | 12 | 11 | 8 | 7 | 4 | 3 |

| 0 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_QUEUE_CNTL1 - Address Offset 07E4h |

|

|

|

|

|

| ||

TX_Queue_Map7 | > | TX_Queue_Map6 | > | |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 |

| 16 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_Queue_Map5 | > | TX_Queue_Map4 | > | |||||

15 | 12 | 11 | 8 | 7 | 4 | 3 |

| 0 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_QUEUE_CNTL2 - Address Offset 07E8h |

|

|

|

|

|

| ||

TX_Queue_Map11 | > | TX_Queue_Map10 | > | |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 |

| 16 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_Queue_Map9 | > | TX_Queue_Map8 | > | |||||

15 | 12 | 11 | 8 | 7 | 4 | 3 |

| 0 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_QUEUE_CNTL3 - Address Offset 07ECh |

|

|

|

|

|

| ||

TX_Queue_Map15 | > | TX_Queue_Map14 | > | |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 |

| 16 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

TX_Queue_Map13 | > | TX_Queue_Map12 | > | |||||

15 | 12 | 11 | 8 | 7 | 4 | 3 |

| 0 |

Number of Msgs |

| Queue Pointer |

|

| Number of Msgs |

| Queue Pointer |

|

|

|

|

|

| ||||

174 | Serial RapidIO (SRIO) | SPRUE13A |

|

| Submit Documentation Feedback |