www.ti.com

SRIO Registers

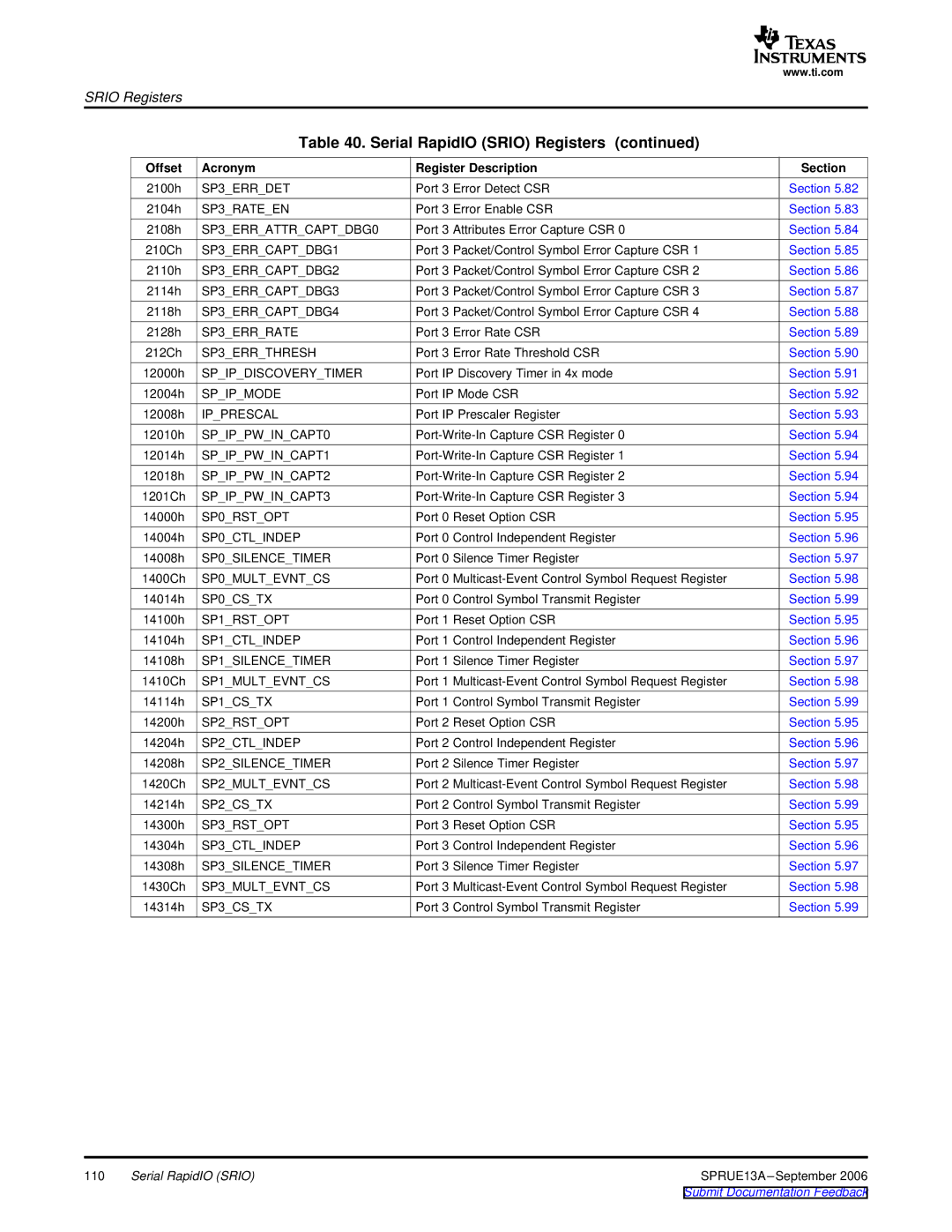

Table 40. Serial RapidIO (SRIO) Registers (continued)

Offset | Acronym | Register Description | Section |

2100h | SP3_ERR_DET | Port 3 Error Detect CSR | Section 5.82 |

2104h | SP3_RATE_EN | Port 3 Error Enable CSR | Section 5.83 |

2108h | SP3_ERR_ATTR_CAPT_DBG0 | Port 3 Attributes Error Capture CSR 0 | Section 5.84 |

210Ch | SP3_ERR_CAPT_DBG1 | Port 3 Packet/Control Symbol Error Capture CSR 1 | Section 5.85 |

2110h | SP3_ERR_CAPT_DBG2 | Port 3 Packet/Control Symbol Error Capture CSR 2 | Section 5.86 |

2114h | SP3_ERR_CAPT_DBG3 | Port 3 Packet/Control Symbol Error Capture CSR 3 | Section 5.87 |

2118h | SP3_ERR_CAPT_DBG4 | Port 3 Packet/Control Symbol Error Capture CSR 4 | Section 5.88 |

2128h | SP3_ERR_RATE | Port 3 Error Rate CSR | Section 5.89 |

212Ch | SP3_ERR_THRESH | Port 3 Error Rate Threshold CSR | Section 5.90 |

12000h | SP_IP_DISCOVERY_TIMER | Port IP Discovery Timer in 4x mode | Section 5.91 |

12004h | SP_IP_MODE | Port IP Mode CSR | Section 5.92 |

12008h | IP_PRESCAL | Port IP Prescaler Register | Section 5.93 |

12010h | SP_IP_PW_IN_CAPT0 | Section 5.94 | |

12014h | SP_IP_PW_IN_CAPT1 | Section 5.94 | |

12018h | SP_IP_PW_IN_CAPT2 | Section 5.94 | |

1201Ch | SP_IP_PW_IN_CAPT3 | Section 5.94 | |

14000h | SP0_RST_OPT | Port 0 Reset Option CSR | Section 5.95 |

14004h | SP0_CTL_INDEP | Port 0 Control Independent Register | Section 5.96 |

14008h | SP0_SILENCE_TIMER | Port 0 Silence Timer Register | Section 5.97 |

1400Ch | SP0_MULT_EVNT_CS | Port 0 | Section 5.98 |

14014h | SP0_CS_TX | Port 0 Control Symbol Transmit Register | Section 5.99 |

14100h | SP1_RST_OPT | Port 1 Reset Option CSR | Section 5.95 |

14104h | SP1_CTL_INDEP | Port 1 Control Independent Register | Section 5.96 |

14108h | SP1_SILENCE_TIMER | Port 1 Silence Timer Register | Section 5.97 |

1410Ch | SP1_MULT_EVNT_CS | Port 1 | Section 5.98 |

14114h | SP1_CS_TX | Port 1 Control Symbol Transmit Register | Section 5.99 |

14200h | SP2_RST_OPT | Port 2 Reset Option CSR | Section 5.95 |

14204h | SP2_CTL_INDEP | Port 2 Control Independent Register | Section 5.96 |

14208h | SP2_SILENCE_TIMER | Port 2 Silence Timer Register | Section 5.97 |

1420Ch | SP2_MULT_EVNT_CS | Port 2 | Section 5.98 |

14214h | SP2_CS_TX | Port 2 Control Symbol Transmit Register | Section 5.99 |

14300h | SP3_RST_OPT | Port 3 Reset Option CSR | Section 5.95 |

14304h | SP3_CTL_INDEP | Port 3 Control Independent Register | Section 5.96 |

14308h | SP3_SILENCE_TIMER | Port 3 Silence Timer Register | Section 5.97 |

1430Ch | SP3_MULT_EVNT_CS | Port 3 | Section 5.98 |

14314h | SP3_CS_TX | Port 3 Control Symbol Transmit Register | Section 5.99 |

110 | Serial RapidIO (SRIO) | SPRUE13A |

|

| Submit Documentation Feedback |