www.ti.com

SRIO Functional Description

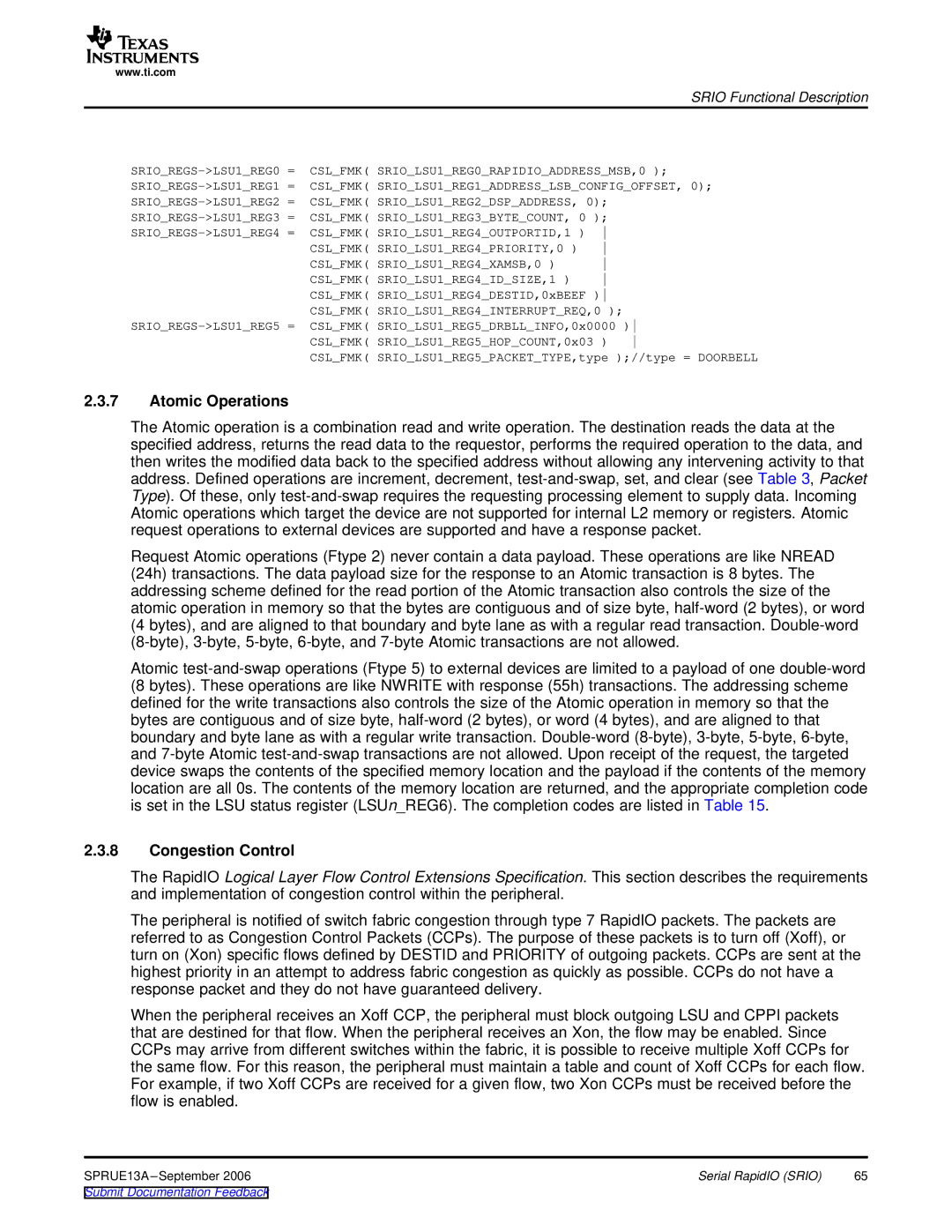

CSL_FMK( SRIO_LSU1_REG0_RAPIDIO_ADDRESS_MSB,0 ); | ||

CSL_FMK( SRIO_LSU1_REG1_ADDRESS_LSB_CONFIG_OFFSET, 0); | ||

CSL_FMK( SRIO_LSU1_REG2_DSP_ADDRESS, 0); | ||

CSL_FMK( SRIO_LSU1_REG3_BYTE_COUNT, 0 ); | ||

CSL_FMK( SRIO_LSU1_REG4_OUTPORTID,1 ) | ||

| CSL_FMK( SRIO_LSU1_REG4_PRIORITY,0 ) | |

| CSL_FMK( SRIO_LSU1_REG4_XAMSB,0 ) | |

| CSL_FMK( SRIO_LSU1_REG4_ID_SIZE,1 ) | |

| CSL_FMK( SRIO_LSU1_REG4_DESTID,0xBEEF ) | |

| CSL_FMK( SRIO_LSU1_REG4_INTERRUPT_REQ,0 ); | |

| CSL_FMK( SRIO_LSU1_REG5_DRBLL_INFO,0x0000 ) | |

| CSL_FMK( SRIO_LSU1_REG5_HOP_COUNT,0x03 ) | |

| CSL_FMK( SRIO_LSU1_REG5_PACKET_TYPE,type );//type = DOORBELL | |

2.3.7Atomic Operations

The Atomic operation is a combination read and write operation. The destination reads the data at the specified address, returns the read data to the requestor, performs the required operation to the data, and then writes the modified data back to the specified address without allowing any intervening activity to that address. Defined operations are increment, decrement,

Request Atomic operations (Ftype 2) never contain a data payload. These operations are like NREAD (24h) transactions. The data payload size for the response to an Atomic transaction is 8 bytes. The addressing scheme defined for the read portion of the Atomic transaction also controls the size of the atomic operation in memory so that the bytes are contiguous and of size byte,

Atomic

2.3.8Congestion Control

The RapidIO Logical Layer Flow Control Extensions Specification. This section describes the requirements and implementation of congestion control within the peripheral.

The peripheral is notified of switch fabric congestion through type 7 RapidIO packets. The packets are referred to as Congestion Control Packets (CCPs). The purpose of these packets is to turn off (Xoff), or turn on (Xon) specific flows defined by DESTID and PRIORITY of outgoing packets. CCPs are sent at the highest priority in an attempt to address fabric congestion as quickly as possible. CCPs do not have a response packet and they do not have guaranteed delivery.

When the peripheral receives an Xoff CCP, the peripheral must block outgoing LSU and CPPI packets that are destined for that flow. When the peripheral receives an Xon, the flow may be enabled. Since CCPs may arrive from different switches within the fabric, it is possible to receive multiple Xoff CCPs for the same flow. For this reason, the peripheral must maintain a table and count of Xoff CCPs for each flow. For example, if two Xoff CCPs are received for a given flow, two Xon CCPs must be received before the flow is enabled.

SPRUE13A | Serial RapidIO (SRIO) | 65 |