www.ti.com

SRIO Registers

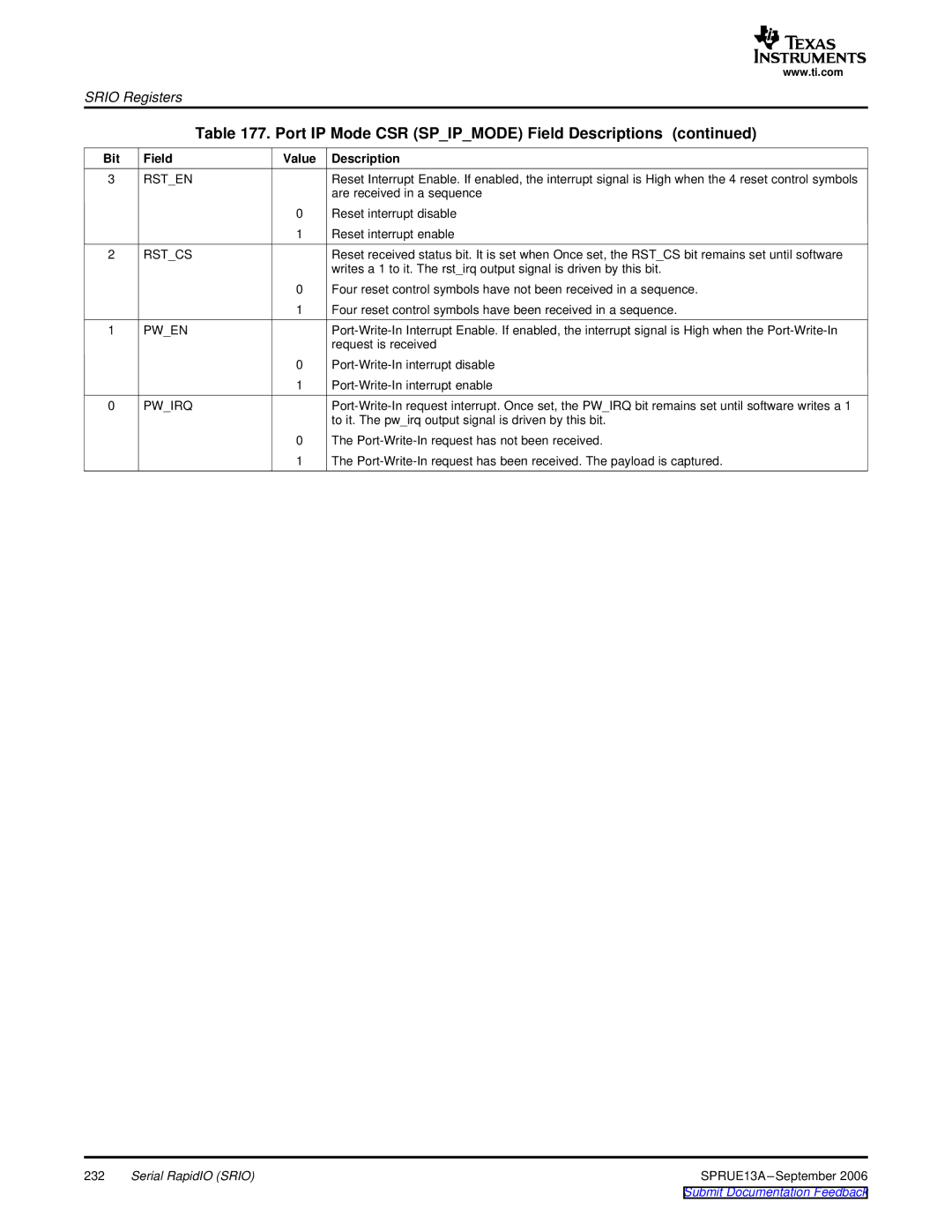

Table 177. Port IP Mode CSR (SP_IP_MODE) Field Descriptions (continued)

Bit | Field | Value | Description |

3 | RST_EN |

| Reset Interrupt Enable. If enabled, the interrupt signal is High when the 4 reset control symbols |

|

|

| are received in a sequence |

|

| 0 | Reset interrupt disable |

|

| 1 | Reset interrupt enable |

2 | RST_CS |

| Reset received status bit. It is set when Once set, the RST_CS bit remains set until software |

|

|

| writes a 1 to it. The rst_irq output signal is driven by this bit. |

|

| 0 | Four reset control symbols have not been received in a sequence. |

|

| 1 | Four reset control symbols have been received in a sequence. |

1 | PW_EN |

| |

|

|

| request is received |

|

| 0 | |

|

| 1 | |

0 | PW_IRQ |

| |

|

|

| to it. The pw_irq output signal is driven by this bit. |

|

| 0 | The |

|

| 1 | The |

232 | Serial RapidIO (SRIO) | SPRUE13A |