www.ti.com

Overview

Features Not Supported:

∙Compliance with the Global Shared Memory specification (GSM)

∙8/16

∙Destination support of RapidIO Atomic Operations

∙Simultaneous mixing of frequencies between 1x ports (all ports must be the same frequency)

∙Target atomic operations (including increment, decrement,

1.3Standards

The SRIO peripheral is compliant to V1.2 of the RapidIO Interconnect Specification and V1.2 of the RapidIO Physical Layer 1x/4x

1.4External Devices Requirements

SRIO provides a seamless interface to all devices which are compliant to V1.2 of the RapidIO Physical Layer 1x/4x

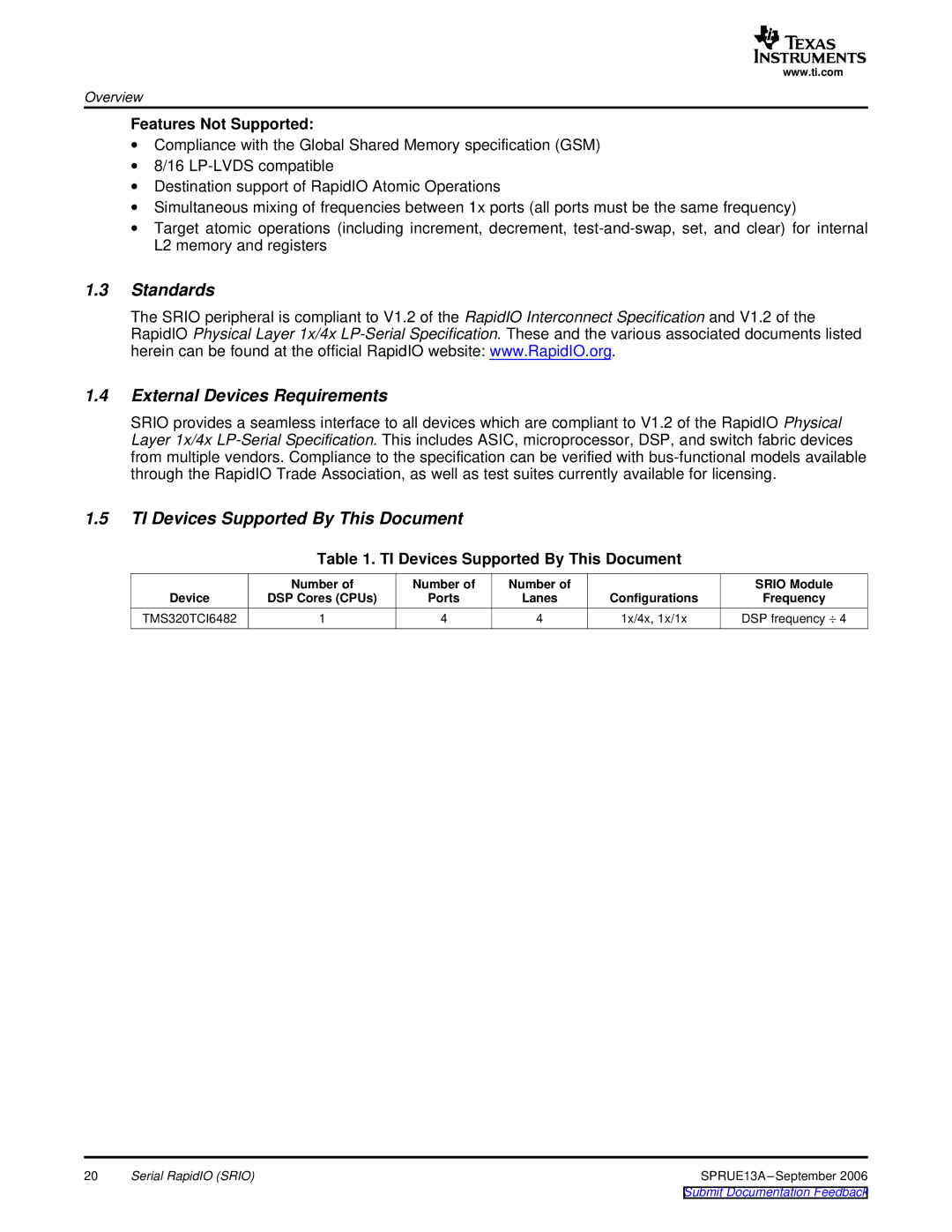

1.5TI Devices Supported By This Document

Table 1. TI Devices Supported By This Document

| Number of | Number of | Number of |

| SRIO Module |

Device | DSP Cores (CPUs) | Ports | Lanes | Configurations | Frequency |

TMS320TCI6482 | 1 | 4 | 4 | 1x/4x, 1x/1x | DSP frequency ÷ 4 |

20 | Serial RapidIO (SRIO) | SPRUE13A |

|

| Submit Documentation Feedback |