www.ti.com

Interrupt Conditions

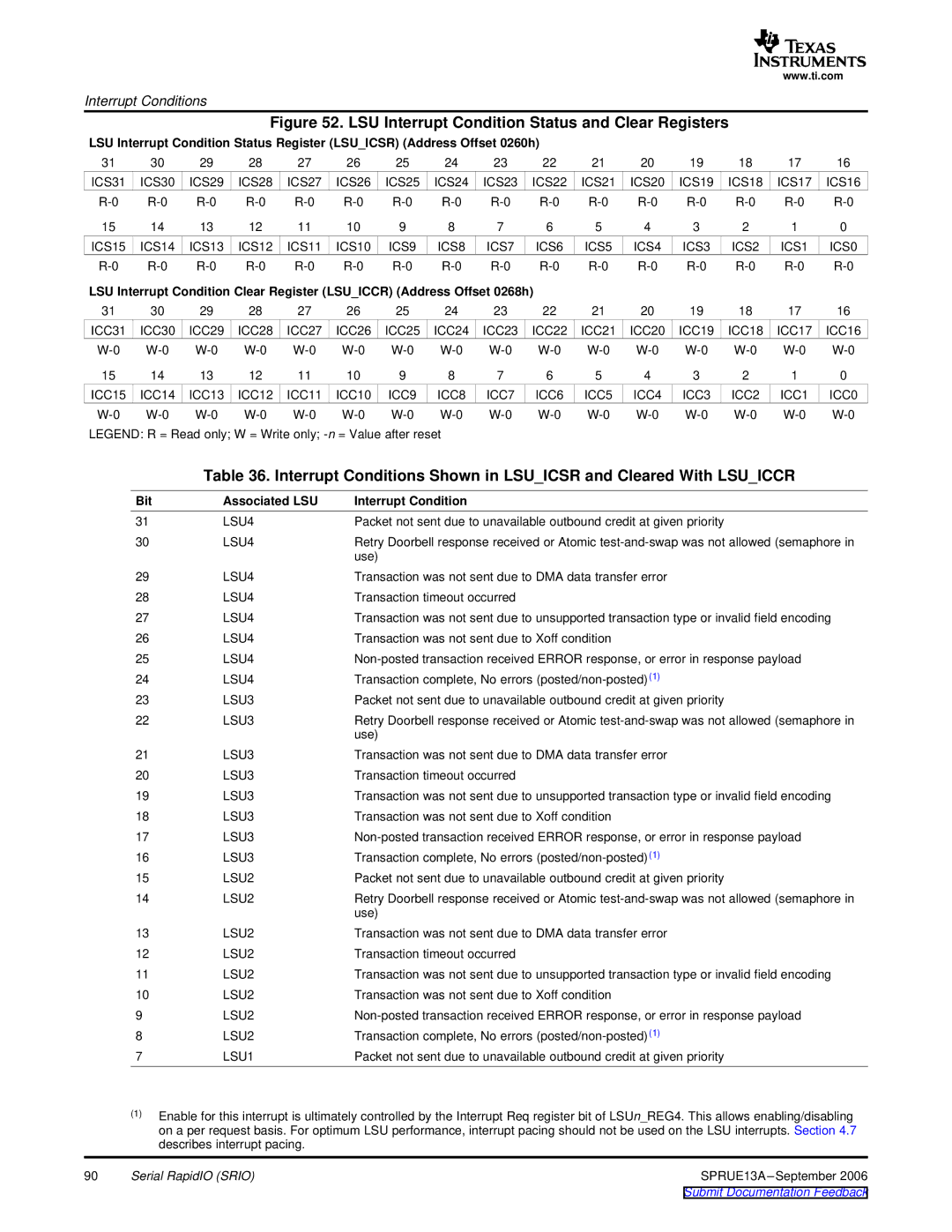

Figure 52. LSU Interrupt Condition Status and Clear Registers

LSU Interrupt Condition Status Register (LSU_ICSR) (Address Offset 0260h) |

|

|

|

|

|

| |||||||||

31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

ICS31 | ICS30 | ICS29 | ICS28 | ICS27 | ICS26 | ICS25 | ICS24 | ICS23 | ICS22 | ICS21 | ICS20 | ICS19 | ICS18 | ICS17 | ICS16 |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

ICS15 | ICS14 | ICS13 | ICS12 | ICS11 | ICS10 | ICS9 | ICS8 | ICS7 | ICS6 | ICS5 | ICS4 | ICS3 | ICS2 | ICS1 | ICS0 |

LSU Interrupt Condition Clear Register (LSU_ICCR) (Address Offset 0268h) |

|

|

|

|

|

| |||||||||

31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

ICC31 | ICC30 | ICC29 | ICC28 | ICC27 | ICC26 | ICC25 | ICC24 | ICC23 | ICC22 | ICC21 | ICC20 | ICC19 | ICC18 | ICC17 | ICC16 |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

ICC15 | ICC14 | ICC13 | ICC12 | ICC11 | ICC10 | ICC9 | ICC8 | ICC7 | ICC6 | ICC5 | ICC4 | ICC3 | ICC2 | ICC1 | ICC0 |

LEGEND: R = Read only; W = Write only; |

|

|

|

|

|

|

|

| |||||||

Table 36. Interrupt Conditions Shown in LSU_ICSR and Cleared With LSU_ICCR

| Bit | Associated LSU | Interrupt Condition |

| 31 | LSU4 | Packet not sent due to unavailable outbound credit at given priority |

| 30 | LSU4 | Retry Doorbell response received or Atomic |

|

|

| use) |

| 29 | LSU4 | Transaction was not sent due to DMA data transfer error |

| 28 | LSU4 | Transaction timeout occurred |

| 27 | LSU4 | Transaction was not sent due to unsupported transaction type or invalid field encoding |

| 26 | LSU4 | Transaction was not sent due to Xoff condition |

| 25 | LSU4 | |

| 24 | LSU4 | Transaction complete, No errors |

| 23 | LSU3 | Packet not sent due to unavailable outbound credit at given priority |

| 22 | LSU3 | Retry Doorbell response received or Atomic |

|

|

| use) |

| 21 | LSU3 | Transaction was not sent due to DMA data transfer error |

| 20 | LSU3 | Transaction timeout occurred |

| 19 | LSU3 | Transaction was not sent due to unsupported transaction type or invalid field encoding |

| 18 | LSU3 | Transaction was not sent due to Xoff condition |

| 17 | LSU3 | |

| 16 | LSU3 | Transaction complete, No errors |

| 15 | LSU2 | Packet not sent due to unavailable outbound credit at given priority |

| 14 | LSU2 | Retry Doorbell response received or Atomic |

|

|

| use) |

| 13 | LSU2 | Transaction was not sent due to DMA data transfer error |

| 12 | LSU2 | Transaction timeout occurred |

| 11 | LSU2 | Transaction was not sent due to unsupported transaction type or invalid field encoding |

| 10 | LSU2 | Transaction was not sent due to Xoff condition |

| 9 | LSU2 | |

| 8 | LSU2 | Transaction complete, No errors |

| 7 | LSU1 | Packet not sent due to unavailable outbound credit at given priority |

| (1) | Enable for this interrupt is ultimately controlled by the Interrupt Req register bit of LSUn_REG4. This allows enabling/disabling | |

|

| on a per request basis. For optimum LSU performance, interrupt pacing should not be used on the LSU interrupts. Section 4.7 | |

|

| describes interrupt pacing. |

|

90 | Serial RapidIO (SRIO) | SPRUE13A | |

|

|

| Submit Documentation Feedback |