www.ti.com

Interrupt Conditions

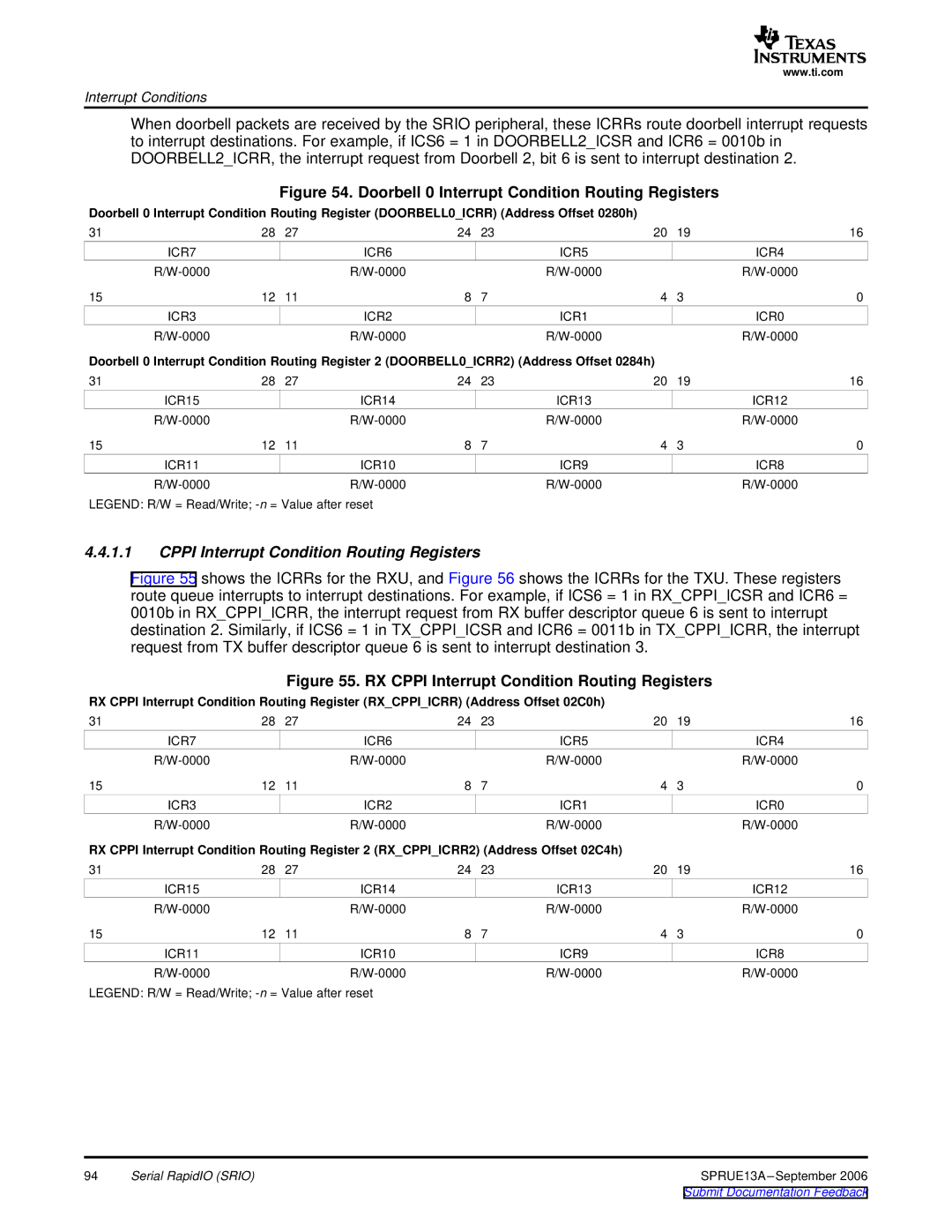

When doorbell packets are received by the SRIO peripheral, these ICRRs route doorbell interrupt requests to interrupt destinations. For example, if ICS6 = 1 in DOORBELL2_ICSR and ICR6 = 0010b in DOORBELL2_ICRR, the interrupt request from Doorbell 2, bit 6 is sent to interrupt destination 2.

Figure 54. Doorbell 0 Interrupt Condition Routing Registers

Doorbell 0 Interrupt Condition Routing Register (DOORBELL0_ICRR) (Address Offset 0280h)

31 | 28 | 27 | 24 | 23 | 20 | 19 | 16 |

| ICR7 |

| ICR6 |

| ICR5 |

| ICR4 |

|

|

|

| ||||

15 | 12 | 11 | 8 | 7 | 4 | 3 | 0 |

| ICR3 |

| ICR2 |

| ICR1 |

| ICR0 |

|

|

|

| ||||

Doorbell 0 Interrupt Condition Routing Register 2 (DOORBELL0_ICRR2) (Address Offset 0284h) |

|

| |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 | 16 |

| ICR15 |

| ICR14 |

| ICR13 |

| ICR12 |

|

|

|

| ||||

15 | 12 | 11 | 8 | 7 | 4 | 3 | 0 |

| ICR11 |

| ICR10 |

| ICR9 |

| ICR8 |

|

|

|

| ||||

LEGEND: R/W = Read/Write;

4.4.1.1CPPI Interrupt Condition Routing Registers

Figure 55 shows the ICRRs for the RXU, and Figure 56 shows the ICRRs for the TXU. These registers route queue interrupts to interrupt destinations. For example, if ICS6 = 1 in RX_CPPI_ICSR and ICR6 = 0010b in RX_CPPI_ICRR, the interrupt request from RX buffer descriptor queue 6 is sent to interrupt destination 2. Similarly, if ICS6 = 1 in TX_CPPI_ICSR and ICR6 = 0011b in TX_CPPI_ICRR, the interrupt request from TX buffer descriptor queue 6 is sent to interrupt destination 3.

Figure 55. RX CPPI Interrupt Condition Routing Registers

RX CPPI Interrupt Condition Routing Register (RX_CPPI_ICRR) (Address Offset 02C0h)

31 | 28 | 27 | 24 | 23 | 20 | 19 | 16 |

| ICR7 |

| ICR6 |

| ICR5 |

| ICR4 |

|

|

|

| ||||

15 | 12 | 11 | 8 | 7 | 4 | 3 | 0 |

| ICR3 |

| ICR2 |

| ICR1 |

| ICR0 |

|

|

|

| ||||

RX CPPI Interrupt Condition Routing Register 2 (RX_CPPI_ICRR2) (Address Offset 02C4h) |

|

| |||||

31 | 28 | 27 | 24 | 23 | 20 | 19 | 16 |

| ICR15 |

| ICR14 |

| ICR13 |

| ICR12 |

|

|

|

| ||||

15 | 12 | 11 | 8 | 7 | 4 | 3 | 0 |

| ICR11 |

| ICR10 |

| ICR9 |

| ICR8 |

|

|

|

| ||||

LEGEND: R/W = Read/Write;

94 | Serial RapidIO (SRIO) | SPRUE13A |

|

| Submit Documentation Feedback |