www.ti.com

SRIO Functional Description

|

|

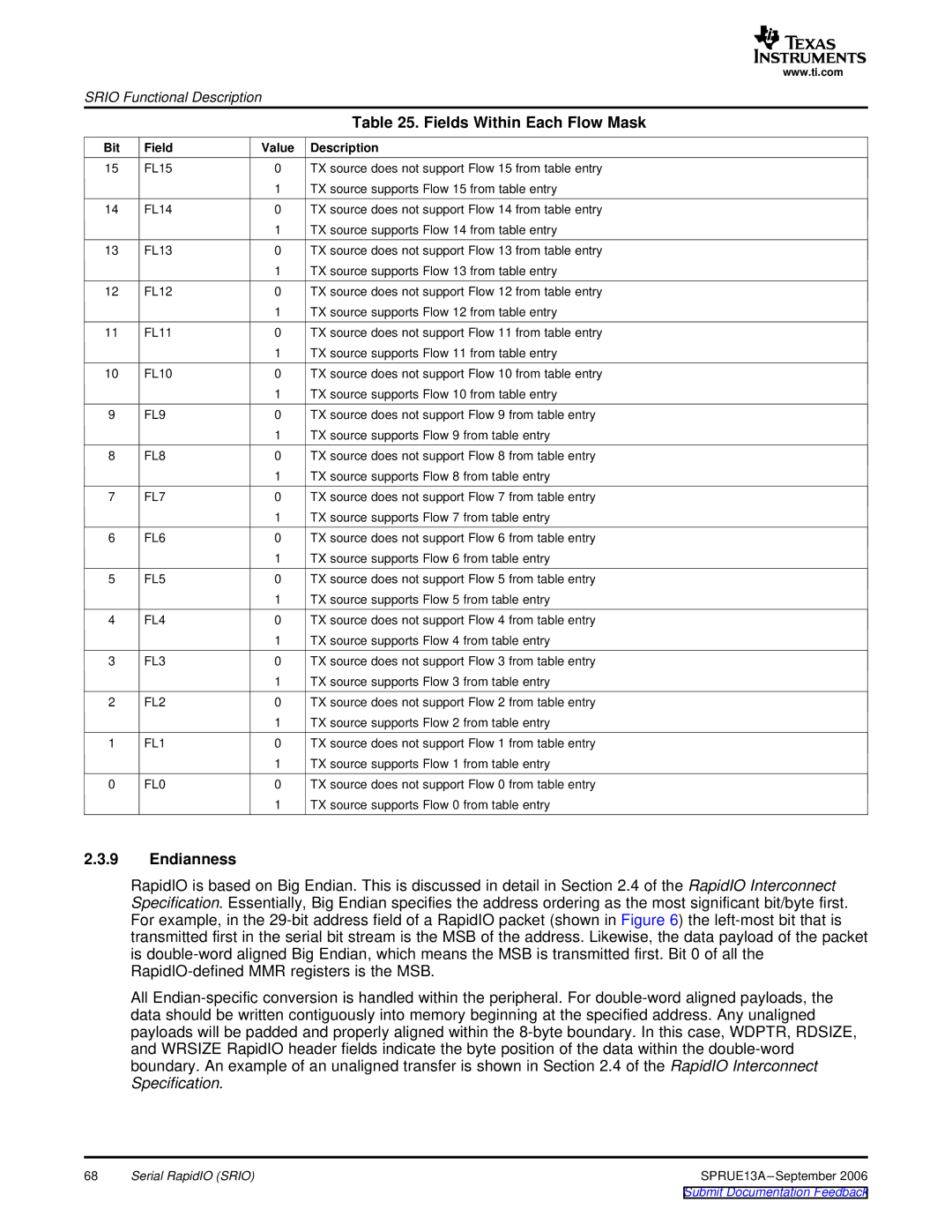

| Table 25. Fields Within Each Flow Mask |

Bit | Field | Value | Description |

15 | FL15 | 0 | TX source does not support Flow 15 from table entry |

|

| 1 | TX source supports Flow 15 from table entry |

14 | FL14 | 0 | TX source does not support Flow 14 from table entry |

|

| 1 | TX source supports Flow 14 from table entry |

13 | FL13 | 0 | TX source does not support Flow 13 from table entry |

|

| 1 | TX source supports Flow 13 from table entry |

12 | FL12 | 0 | TX source does not support Flow 12 from table entry |

|

| 1 | TX source supports Flow 12 from table entry |

11 | FL11 | 0 | TX source does not support Flow 11 from table entry |

|

| 1 | TX source supports Flow 11 from table entry |

10 | FL10 | 0 | TX source does not support Flow 10 from table entry |

|

| 1 | TX source supports Flow 10 from table entry |

9 | FL9 | 0 | TX source does not support Flow 9 from table entry |

|

| 1 | TX source supports Flow 9 from table entry |

8 | FL8 | 0 | TX source does not support Flow 8 from table entry |

|

| 1 | TX source supports Flow 8 from table entry |

7 | FL7 | 0 | TX source does not support Flow 7 from table entry |

|

| 1 | TX source supports Flow 7 from table entry |

6 | FL6 | 0 | TX source does not support Flow 6 from table entry |

|

| 1 | TX source supports Flow 6 from table entry |

5 | FL5 | 0 | TX source does not support Flow 5 from table entry |

|

| 1 | TX source supports Flow 5 from table entry |

4 | FL4 | 0 | TX source does not support Flow 4 from table entry |

|

| 1 | TX source supports Flow 4 from table entry |

3 | FL3 | 0 | TX source does not support Flow 3 from table entry |

|

| 1 | TX source supports Flow 3 from table entry |

2 | FL2 | 0 | TX source does not support Flow 2 from table entry |

|

| 1 | TX source supports Flow 2 from table entry |

1 | FL1 | 0 | TX source does not support Flow 1 from table entry |

|

| 1 | TX source supports Flow 1 from table entry |

0 | FL0 | 0 | TX source does not support Flow 0 from table entry |

|

| 1 | TX source supports Flow 0 from table entry |

2.3.9Endianness

RapidIO is based on Big Endian. This is discussed in detail in Section 2.4 of the RapidIO Interconnect Specification. Essentially, Big Endian specifies the address ordering as the most significant bit/byte first. For example, in the

All

68 | Serial RapidIO (SRIO) | SPRUE13A |