www.ti.com

SRIO Functional Description

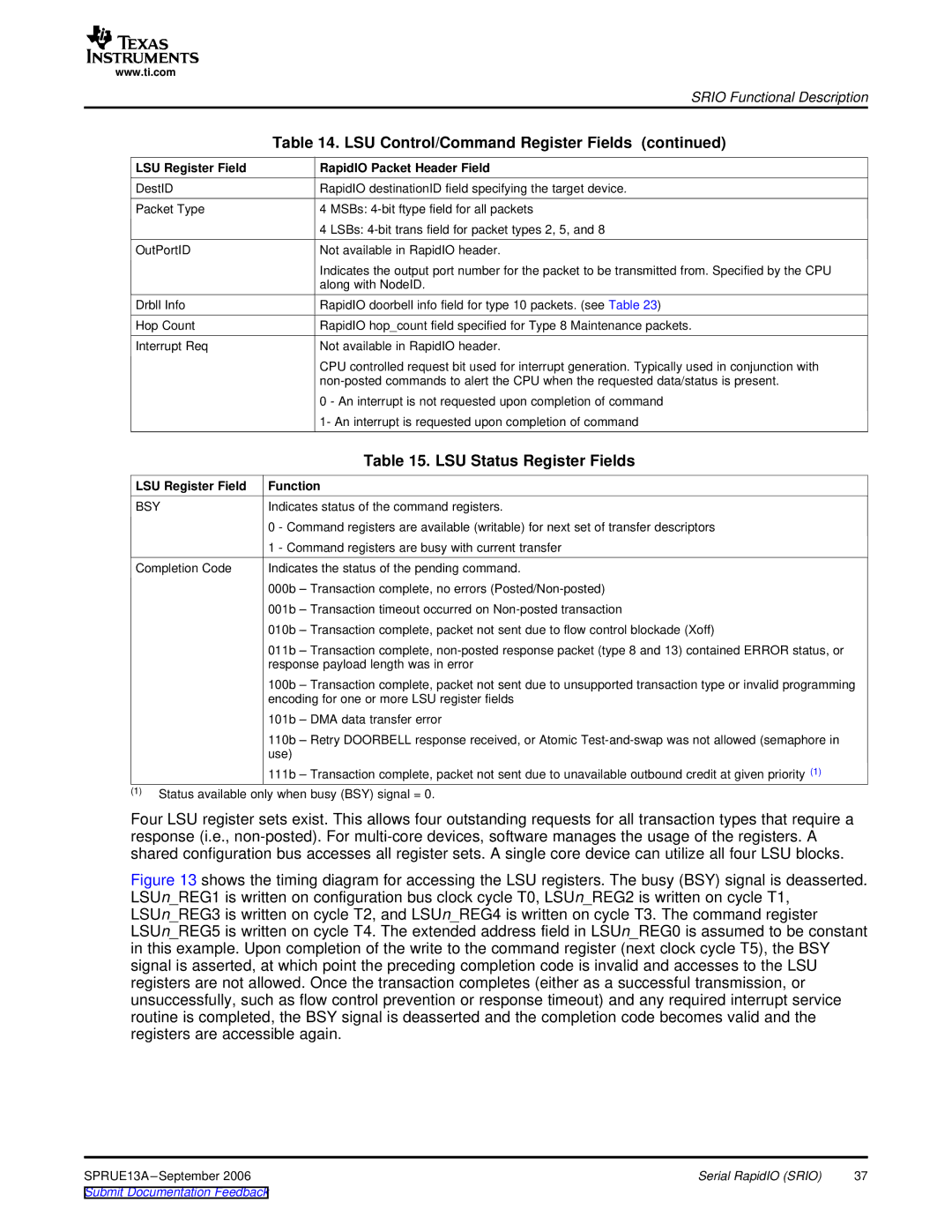

| Table 14. LSU Control/Command Register Fields (continued) |

LSU Register Field | RapidIO Packet Header Field |

DestID | RapidIO destinationID field specifying the target device. |

Packet Type | 4 MSBs: |

| 4 LSBs: |

OutPortID | Not available in RapidIO header. |

| Indicates the output port number for the packet to be transmitted from. Specified by the CPU |

| along with NodeID. |

Drbll Info | RapidIO doorbell info field for type 10 packets. (see Table 23) |

Hop Count | RapidIO hop_count field specified for Type 8 Maintenance packets. |

Interrupt Req | Not available in RapidIO header. |

| CPU controlled request bit used for interrupt generation. Typically used in conjunction with |

| |

| 0 - An interrupt is not requested upon completion of command |

| 1- An interrupt is requested upon completion of command |

|

| Table 15. LSU Status Register Fields |

LSU Register Field | Function | |

BSY | Indicates status of the command registers. | |

| 0 - Command registers are available (writable) for next set of transfer descriptors | |

| 1 - Command registers are busy with current transfer | |

Completion Code | Indicates the status of the pending command. | |

| 000b | – Transaction complete, no errors |

| 001b | – Transaction timeout occurred on |

| 010b | – Transaction complete, packet not sent due to flow control blockade (Xoff) |

| 011b | – Transaction complete, |

| response payload length was in error | |

| 100b | – Transaction complete, packet not sent due to unsupported transaction type or invalid programming |

| encoding for one or more LSU register fields | |

| 101b | – DMA data transfer error |

| 110b | – Retry DOORBELL response received, or Atomic |

| use) |

|

| 111b | – Transaction complete, packet not sent due to unavailable outbound credit at given priority (1) |

(1)Status available only when busy (BSY) signal = 0.

Four LSU register sets exist. This allows four outstanding requests for all transaction types that require a response (i.e.,

Figure 13 shows the timing diagram for accessing the LSU registers. The busy (BSY) signal is deasserted. LSUn_REG1 is written on configuration bus clock cycle T0, LSUn_REG2 is written on cycle T1, LSUn_REG3 is written on cycle T2, and LSUn_REG4 is written on cycle T3. The command register LSUn_REG5 is written on cycle T4. The extended address field in LSUn_REG0 is assumed to be constant in this example. Upon completion of the write to the command register (next clock cycle T5), the BSY signal is asserted, at which point the preceding completion code is invalid and accesses to the LSU registers are not allowed. Once the transaction completes (either as a successful transmission, or unsuccessfully, such as flow control prevention or response timeout) and any required interrupt service routine is completed, the BSY signal is deasserted and the completion code becomes valid and the registers are accessible again.

SPRUE13A | Serial RapidIO (SRIO) | 37 |