Page

DVP-ES2/EX2/SS2/SA2/SX2/SE

FLD=, FAND=, FAND, FAND, Fand

Page

Contents

Communications

Appendix a

Series Model name

Page

PLC Concepts

PLC Scan Method

Scan time exception

Current Flow

No Contact, NC Contact

Reverse Current

PLC Registers and Relays

Ladder Logic Symbols

Creating a PLC Ladder Program

ORB ANB

TMR

2 LD / LDI Load no contact / Load NC contact

ANB Connect block in series

ORB Connect block in parallel

MPS / MRD / MPP Branch instructions

Branch Description Instruction Symbol

MPS

STL Step Ladder Programming

S21 S22

RET Return

Conversion between Ladder Diagram and Instruction List Mode

Ladder Diagram

Example Better method OK method

Common Programming Errors

Fuzzy Syntax

Example Good method Bad method

Or operation upward is not allowed Reverse current exists

LD T0 X2 ORB

Correcting Ladder Diagram

Example

Or T0

MPS OUT MPP

OUT Y0 Y1 and X0 OUT Y1

Basic Program Design Examples

Example 1 Stop First latched circuit

Stop

Example 4 Power down latched circuit

Example 2 Start First latched circuit

Example 3 Latched circuit of SET and RST

Example 6- Interlock control

Example 7 Sequential Control

Example 8 Oscillating Circuit

Example 10 Flashing Circuit

Example 9 Oscillating Circuit with Timer

Example 12 Delay OFF Circuit

Example 11 Trigger Circuit

Example 13 Output delay circuit

Example 14 Timing extension circuit

Example 15 Counting Range Extension Circuit

Green light Blinking

Timing Diagram

Green light

SFC Figure

Ladder Diagram

WPLSoft programming SFC mode

Memo

Programming Concepts

Specifications

ES2/EX2 Memory Map

Programming Concepts

Specifications

SS2 Memory Map

Specifications

Specifications

SA2 Memory Map

Specifications

Specifications

SX2 Memory Map

Specifications

Specifications

Status and Allocation of Latched Memory

STOP=RUN RUN=STOP

OFF=ON

PLC Bits, Nibbles, Bytes, Words, etc

Binary, Octal, Decimal, BCD, Hex

BCD

BIN OCT DEC

HEX

Relay

EX2 RUN Stop

Latch Default Function

M1052 Disable interruption I200

OFF PCC01

M1109 Y1 pulse output pause ramp down

M1141 For COM2 RS-485, Modrd / Modwr

M1203 C203 counting mode on count down

M1233 C233 counter monitor on count down

M1274 C239 counting mode on falling-edge

OFF YES

M1378 Indicate Slave ID#3 data interchange

Latch Default

Attrib Latch Default

Timer

Counter

Accumulative Timer

Timers for Subroutines and Interrupts

Bits Bits counters Counters

RST CNT OUT

OUT Y0

Plus 1 or count down minus

High-speed Counters

Applicable Software High Speed Counters

Applicable Hardware High Speed Counters

Phase 1 input high-speed counter Example

RST

Dcnt

Phase 2 inputs high-speed counter Example

AB-phase input high-speed counter Example

MOV

Special Data Register

0FDB

D1031 PV of Y0 pulse output High word

YES ’FFFF

COM2RS-485 Definition of start character STX ’3A

D1240 stores the low word of high-speed counter

D1314 Minute of RTC 00 ~

’1064

Link

D1442 Data length to be read on Slave ID#9

PLC Link

D1767 D1768 Data which is read from slave ID#10

DVP-PCC01

Index register E, F

14 E, F Index Registers

Nest Level PointerN, PointerP, Interrupt Pointer

Call

CJ P1

Call

Page

Applications of Special M Relays and D Registers

Number D1002 Contents

Function Group Watchdog Timer Number M1008, D1008 Contents

Function Group High-speed Timer Number M1015, D1015 Contents

Function Group Number D1018~D1019 Contents

Device Name Function

Number D1020 Contents

Number M1083,M1084, D1023 Contents

Incd

MTR, HKY, DSW, SEGL, PR

PLSY, Plsr

RAMP, Sort

ZRN, DRVI, Drva

Number M1034 Contents

Dabsr

Device Devices will be cleared

Port

Function Group RUN/STOP Switch Number M1035 Contents

Content

COM1 COM2 COM3

COM3

Example 1 Modifying COM1 communication format

Example 2 Modiying COM2 communication format

Example 4 RTU mode setting of COM1、COM2、COM3

Example 3 Modifying COM3 communication format

Number M1037, D1037 Contents

Number D1038 Contents

Function Group Fixed scan time Number M1039, D1039 Contents

Number D1062, D1110~D1113, D1116~D1118 Contents

Device Function

0xF

Number M1119 Contents

Contents Device Explanation Latched

Error code explanation D1067 error code Function

STOP→RUN RUN→STOP

Number M1280, M1284, M1286 Contents

Number M1304 Contents

Number M1308, D1312 Contents

Number D1320~ D1327 Contents

Number M1346 Contents

Function Group PLC Link Number

Master PLC Slave ID

Read Write Out D100 D200

M1376 M1377 M1378 M1379 M1380 M1381 M1382 M1383

M1416 M1417 M1418 M1419 M1420 M1421 M1422 M1423

Page

Programming Concepts

Operation flow chart

Programming Concepts

SET MOV

Programming Concepts

Memo

Instruction Set

Basic Instructions without API numbers

Execution speed Instruction Function Operand Steps

ES2/EX2/SS2 SA2/SX2

Explanations to Basic Instructions

LDI

Connect no contact Parallel Controllers

ANI

Connect NC contact Series Controllers

ORI

Connect a block in series Controllers

Mnemonic Function Program steps

ANB

ORB

Explanations Controllers

Points to note

MPP

MPS

MRD

OUT

Device Status

SET

Latches the on Status Controllers

RST

MCR

NOP

END

Program End Controllers

No operation Controllers

Scan cycle

P10

Pointers

Interrupt Pointers

Fend

External interrupt

Timer Interrupts

Iret

Communication Interrupts

Mnemonic Operands Function Controllers

Application Programming Instructions

API

Type Bit Devices Word devices Program Steps

Length of Operand 16-bit or 32-bit instruction

Explanation of the format of application instruction

Continuous execution vs. Pulse execution

Operand Data format

Kn values Bit instruction

Flags Bit instruction

Limitations for times of using instructions

API 155 Dabsr

Limitation of synchronized execution

Numeric Values

Assign Continuous Bit Numbers

Floating Point Operation

Example 2 Represent -23.0 in 32-bit floating point value

Binary Floating Point

Example 1 Represent 23 in 32-bit floating point value

Decimal Floating Point

Bit 16-bit 32-bit

Instruction Set

Loop Control

Transmission Comparison

Four Arithmetic Operations

Rotation and Displacement

Data Processing

High Speed Processing

Handy Instructions

External I/O Display

Serial I/O

Basic Instructions

PLF

Falling-edge output Communication Instructions

Additional Instruction

Positioning Control

Real Time Calendar

Gray Code

Matrix Operation

Contact Type Logic Operation

S1 S2 Contact Type Comparison

223

DOR

Specific Bit Control

Numerical List of Instructions in alphabetic order

ABS Dabs

Absd Dabsd

Alternate state 218

Connect NC contact in parallel By specified bit 266

GPS data receiving 144

PLF

Pulse output Print Ascii code output

Stop VFD

Axis Relative Position Arc Interpolation 197

Single-Axis pulse output by 116

Detailed Instruction Explanation

Range

CJ P1

M4 on

OFF→ON

ON→OFF M4 OFF M4 OFF→ON

M4 on OFF

CNT

CALL, Callp 3 steps

Subroutine Return

Mnemonic Function

Sret

Descriptions Program Steps

INC

Iret

Mnemonic Function Enable Interrupt Controllers

Mnemonic Function Disable Interrupt Controllers

Interrupt Return

Flag Function

101

Fend

End of The Main Program First End

No contact to drive the instruction is required

CJ Instruction Program Flow

Call Instruction Program Flow

WDT, Wdtp 1 step

WDT

KnX KnY KnM KnS T For 3 steps

For K3 For K4 Next

TMR

CMP

Mnemonic Operands Function

ZCP

RST M0 RST M1 RST M2 Zrst M0 M2

KnX KnY KnM KnS T MOV, Movp 5 steps

Shift

Smov

PLC

CML

BMOV, Bmovp 7 steps

Bmov K1M0 K1Y0

Fmov

DFMOV, Dfmovp

XCH

BCD

BIN

103 102 101 Digit DIP switch in BCD format

ADD

Operation of flags

Zero flag

SUB

16-bit BIN subtraction

MUL

MUL D0 D10 D20

DIV

B00 B15

INC

DEC

D2 0

Wand

Dand

WOR

Logical Word or

Logical DWord or

DOR

Wxor

Logical Word XOR

Dxor

NEG

D0=2 0 0

ROR

ROL

RCR

RCL

KnX KnY KnM KnS T SFTR, Sftrp 9 steps

Sftr

Wsfr

Word Shift Right

Wsfrp K1X20 K1Y20

Wsfl

Word Shift Left

KnX KnY KnM KnS SFWR, Sfwrp 7 steps

Sfrd

Shift Register Read

KnX KnY KnM KnS T ZRST, Zrstp 5 steps

RST M0 RST T0 RST Y0

KnX KnY KnM KnS DECO, Decop 7 steps

D10 D20 B15 All be

All be B15

D10

SUM

BON

Mean

DMEAN, Dmeanp

ANS T10 K50 S999

Application example of alarm device production line

Instruction driven by contact is necessary

Points to note Flags

ANS

SQR

FLT

Apply FLT instruction to complete the following operation

FLT

KnX KnY KnM KnS T REF, Refp 5 steps

SET M1180

KnX KnY KnM KnS T REFF, Reffp 3 steps

MTR

MTR

Points to note

Hscs

Instruction Set

Page

Counting

Dhscs K100

Fend

API Mnemonic Operands Function Controllers

Hscr

HSZ

High Speed Zone

Compare Type Bit Devices Word devices Program Steps

Page

Program Example 1 Applying Hardware High Speed Counter

Dhsz

Speed variable

KnX KnY KnM KnS T SPD 7 steps

⋅10 3 rpm n

SA2/SE/SX2

Plsy

Pulse Output

CCW

200

Page

SET M1347 Plsy K1000 K1000 Y0

KnS PWM 7 steps

=1000ms Output Y1 =2000ms

Page

Plsr

Pulse Ramp

Page

Frequency Increased/decreased Every shift 1000/20 Hz

Explanations on associated flags and registers

Frequency Target

Explanations

Pulse

Explanations

KnX KnY KnM KnS T IST 7 steps

Sensor

Control panel

S10 S11 S12

S20 Y1

RET END

M1042

Flag explanation M1040

M1041

M1043

M1046

M1047

D1040~D1047

SER

Absd

Lower-bound value Upper- bound value Current value of C10

Bit Devices Word devices Program Steps

Page

KnX KnY KnM KnS T C Ttmr 5 steps

D0 unit sec Unit 100 ms

Special Timer

Stmr

X20 Y3 Stmr T10 K50 Y0

KnX KnY KnM KnS T ALT, Altp 3 steps

Ramp

If X20 = on

DTM

Data Transform

Move Type Bit Devices Word devices Program Steps

E f

+10

Instruction Set

+1 S S+2

Combination will be performed in the following rule

‘1’ ‘2’ ‘3’ ‘.’ ‘4’ ‘5’ ‘6’ 0x00

Program Example 1 K2, K4

Program Example 2 K9

Page

Sort

Data sort

Example table of data sort

TKY

BCD value 1-digit BCD code Overflow 103 102 101 BIN value D0

HKY

Input keys 0~9

PLCTransistor output

KnX KnY KnM KnS T DSW 9 steps

PLC

KnX KnY KnM KnS T SEGD, Segdp 5 steps

Segl

Segment with Latch

192

BCD value Output BCD code Signal output

PLC

194

Arrow switch

Arws

Arws

ASC

Ascii code conversion

KnX KnY KnM KnS T PR 5 steps

X20 drive signal

From

DFROM, Dfromp

ES2/EX2 SS2 SA2/SE/SX2

Rules for operand

Upper 16-bit Lower 16-bit CR #10 CR #9 Specified CR number

Mnemonic Operands Function Controllers Serial Communication

Program Example 1 COM2 RS-485

Bit mode

Program Example 2 COM2 RS-485

Receiving data External equipment PLC

ADR

Program Example 3 COM2 RS-485

STX

CMD

D120 high ‘0’ 30 H

Program Example 4 COM2 RS-485

Program Example 5 COM1 RS-232

Receving data External equipment→PLC

Program Example 6 COM3 RS-485

Flag Function Action

Special register Function

Function Action

Modrd / Modwr / FWD / REV / Stop / Rdst / Rstef

Modrd / MODWR/ Modrw

Modrd / Rdst / Modrw

Modrd / Modwr / Modrw

FWD / REV / Stop / Rdst / Rstef

REV / Stop / Rdst / Rstef / Modrw

Data sending and receiving will be started. When

Protocol

Setting

Function Description

Sending

Receiving

Errors

Data

Completed

FWD/REV/STOP/RDST/RSTEF

ETX1

ETX2

Value Error Description

M1130

M1126

COM1

Ascii mode Field Name Descriptions

COM Port I10 interrupt Special D

COM2

Field Name Descriptions

RTU mode

CR LF

Start

START/END

Field Name Data Hex

Example program of RS-485 communication

Reset in program

Prun

DPRUN, Dprunp

Asci

Convert Hex to Ascii

= Cdef H

When n is 6, the bit structure will be as

= Cdefh

When n is 4, the bit structure will be as

Instruction Set

Convert Ascii to HEX

Ascii code

Conversion

CDE H

Cdef H

DEF8 H

D20 D21

CCD

Check Code

Parity

Volume Read

Vrrd

Volume Scale Read

Vrsc

ABS

PID

Device Function Setup Range Explanation

Reverse control E = PV SV

Device Function Set-point range Explanation

Proportion for

PID Equations

MV = KP * Et + KI * EtS1 + KD * PV t S

⎢Et +

Position instruction

=40 SV=1 KP =20 KP =10 KP =5

Step

Application

Example program of SV ramp up function

PID

Part of the example program

From

Auto tuning area S3+4 = k3 PID control area S3+4 = k4

Instruction Set

PLS

LDP

Rising-edge detection operation

LDF

Andp

Rising-edge series connection

Andf

ORP

Rising-edge parallel connection

ORF

Falling-edge parallel connection

TMR

T5 K1000

CNT

C20 K100

Dcnt

C254 K1000

INV

Inverse operation

KnX KnY KnM KnS T C PLF 3 steps

Read Modbus Data

Register Data Descriptions

Modrd

Registers for received data responding messages

K100 D1129 Sett receiving timeout as 100ms

FE H

Modrd K1

Write Modbus Data

D1089 low ‘0’ 30 H

D1070 low ‘0’ 30 H

Register Data Descriptions

M1002 Set communication protocol as 9600, 8, E

VFD

Program Example COM2 RS-485

FWD

Register Data Descriptions

PLC

VFD, PLC sends 01 10 2000 0002 04 0012 01F4 C2

Data Descriptions

Error checksum LRC CHK

B, Uu, Nn, Abcd

GFF

HPF

Range of S1 K1 ~ K255

‘0’ 30 H Number of data count by word ‘5’ 35 H ‘D’ 44 H

Reset Abnormal VFD

Rstef

‘2’ 32 H ‘0’ 30 H Data address Data content ‘D’ 44 H

KnX KnY KnM KnS T LRC, Lrcp 7 steps

08 0006 E7 CR LF

Register Data Explanation

Remarks

KnX KnY KnM KnS T C CRC, Crcp 7 steps

01 06 0706 1770 66 AB

Ecmp

DECMP, Decmpp

Ezcp

DEZCP, Dezcpp

Movr

DMOVR, Dmovrp

RAD

DEG

Ebcd

DEBCD, Debcdp

Ebin

K314

Eadd

DEADD, Deaddp

Esub

DESUB, Desubp

Emul

DEMUL, Demulp

Ediv

EXP

125 Float natural logarithm operation

LOG

Dflt D0 D10 Dflt D2 D12

Esqr

DESQR, Desqrp

POW

DPOW, Dpowp

Dpow D10 D12 D20

KnX KnY KnM KnS T INT, Intp 5 steps DINT, Dintp 9 steps

SIN

Movp

COS

Degree value

TAN

TAN value

Asin

D11 D10 Asin value Binary floating point

Acos

DACOS, Dacosp

D11 D10 Acos value Binary floating point

Mnemonic Operands Function 135

Arc Tangent

DATAN, Datanp

DELAY, Delayp

General PWM output

Swap

DSWAP, Dswapp

Memr K10 D2000 K100

Writing the data into

PLC COM COM1 COM2 COM3

COM1 RTU COM2 COM3 Ascii

COM

H0F

Program Example 1 COM2RS-485, Function Code H02

Ascii Mode M1143 = OFF

Modrw

RTU Mode M1143 = on

Program Example 2 COM1RS-232 / COM3RS-485, Function Code H02

MOV

COM2 COM1 COM3

Program Example 3 COM2 RS-485, Function Code H03

D1256 Low byte ‘0’ 30 H

D1262 High byte ‘5’ 35 H

CF H

Program example 4 COM1RS-232 / COM3RS-485, Function Code H03

Ascii mode COM3 M1320 = OFF, COM1 M1139 = OFF

Modrw

RTU mode COM3 M1320 = on COM1 M1139 = on

Program example 5 COM2RS-485, Function Code H05

CMD 1,0 Control parameter

FF H

Program example 6 COM1RS-232 / COM3RS-485, Function Code H05

RTU mode COM3 M1320 = ON, COM1 M1139 = on

Program Example 7 COM2RS-485, Function Code H06

VFD-B Ö PLC, PLC receives 01 06 2000 1770

RTU mode M1143 = on

Program Example 9 COM2 RS-485, Function Code H0F

D1256 下 ‘0’ 30 H

PLC1 Ö PLC2,PLC1 sends 01 0F 0500 0010 02 34 12 21 ED

ED H

CB H

M1002 D1109 Set communication protocol as 9600, 8, E

Program Example 11 COM2 RS-485, Function Code H10

LRC CHK 0,1 is error check

PLC ÖVFD-B,PLC transmits 01 10 2000 0002 04 1770 0012 EE 0C

EE H

M1320 M1320 = OFF

Rand

DRAND, Drandp

TLC SON Absm Absr

Absr

Timing diagram of the operation of Dabsr instruction

Ex Mitsubishi MR-J2-A CR 8 reset

ZRN

Page

Time

Freq

Time

Freq

MOV K-2 D1312 RST M1308 SET M1346 Dzrn K20000 K1000 X4 Y0

Plsv

Drvi

M10 Ddrvi K20000 K2000 Y0

Page

Instruction Set

Drva

M10 Drva K20000 K2000

Page

Mnemonic Operands Function 160

Tcmp

Time compare

Mnemonic Operands Function Controllers 161

Tzcp

Time zone compare

Tadd

Time addition

KnX KnY KnM KnS TSUB, Tsubp 7 steps

D10 D20 05Hour

Special D Content

Normal D

Device Content Function

Device Content Range

RTC

Normal D Range

Program Example Special D

TWR

MVM

DMVM,DMVMP

Hour

Y10 Dhour K40000 D0

GRY

Gbin

DGBIN, Dgbinp

Addr

DADDR, Daddrp

Daddr D0 D2 D10

Subr

Dsubr D0 D2 D10

Mulr

DMULR, Dmulrp

Dmulr D0 D10 D20

Divr

When X23 = 0N, 16-bit data in D4 will be sent to D6 and D7

GPS data receiving

GPS data valid / invalid

K2000 D1249 Set receiving time-out as 2s

GND

Page

SPA

Page

M0 M1013 Dspa D4000 D5000

Wsum

DWSUM, Dwsump

Mand

Matrix

Fill 0 into the blank in R0C15-C8, R1C15-C8, and R2C15-C8

MOR

Matrix or

Mxor

Mxnr

Matrix XNR

Minv

Mcmp

Matrix compare

Mcmp

Matrix bit read

B47 Pointer D20

Matrix bit write

Before Execution After

MBS

Matrix bit shift

MBS

MBR

Matrix bit rotate

MBR

D10 12 M1098=0 D10 36 M1098=1

Ppmr

Draw a rhombus as the figure below

Dppmr

Axis Absolute Point

Dppma

Cimr

Quadrant

Draw an ellipse as the figure below

Draw a tilted ellipse as the figure below

Points to note

Cima

Dcima

RST

Ptpo

Dptpo D0 D300 Y0

Cllm

Close Loop Explanations

Instruction Set

100kHz X4 = OFF -- on

Assume the first execution results are as below

Points to note

Reset after CH0 Y0, Y1 pulse output is completed

Vspo

Function Explanations

Freq Time Pulse number

Freq T2=11kHz

Instruction Set

Mnemonic Operands Function 199

ICF

Immediately change frequency

Interrupt

M0=ON X6=ON X7=ON

Dvspo

Destination value

Scal K500 K-168 K534 D10

Floating point number

Device No Parameter Range

Device No Parameter Range Integer S2、S2+1

= kx + b

Destination value Max. Destination value Source value

Destination value =500 Source value

Dmovr F200 D2 Dmovr F500 D4 Dmovr F30 D6

Cmpt

Cmpt

Asda servo drive

Program example 1 COM2 RS-485

Program example 2 COM3RS-485

Asdrw

COM2 COM3

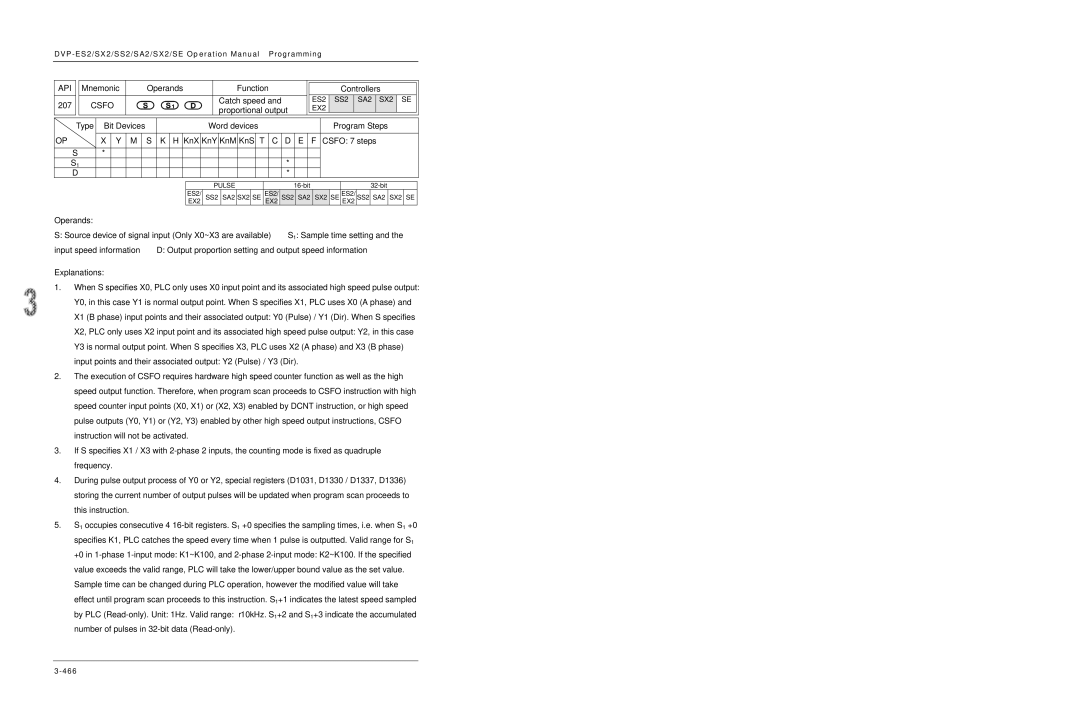

Csfo

Catch speed

Proportional output

Csfo X1 D0 D10

DLD

Dand

AND#

Serial Type Logic Operation

219

OR#

Operands S1 Source device S2 Source device Explanation

222

LD※

Dand =

Dand >

Dand <

OR※

Parallel Type Comparison

Bout

K4Y0 D0 When D0 = k1

Executes output on Y1 When D0 = k2, executes output on Y2

Bout

Bset

Bset

Program Example Instruction Operation

K4Y0 D0 When D0 = k1 Y1 is OFF When D0 = k2 Y2 = OFF

Brst

Load no contact

K3 Load no contact with bit

BLD

BLD

Status of bit3 in D0

K1 Load NC contact with bit

Bldi

Bldi

Status of bit1 in D0

Band

Band

Bani

Bani

K0 Connect NC contact in series

K0 Connect no contact

BOR

BOR

Defined by bit0 of D0

Bori

Bori

K0 Connect NC contact

FLD >

FLD※

FLD =

FLD <

Fand <

Fand =

Fand >

Fand <>

For =

For >

For <

Memo

Communications

Communication Ports

END1

Communication Protocol Ascii mode

CMD Command code and Data

END0

Ascii

CMDHex Explanation Device

PC→PLC

END CR LF

LRC CHK checksum

Exception response

Start

Communication Protocol RTU mode

Exception Explanation Code

Address Communication Address

Field Name Example Hex

CRC CHK check sum

Exception response

ES2/EX2 SS2 SA2/SE

PLC Device Address

Modbus

SX2

A710~AEDF

Command Code

ETX

Ascii

Command Code 03, Read Content of Register T, C, D

Command Code 05, Force ON/OFF single contact

Force Data Lo Error Check LRC

Command Code 15, Force ON/OFF multiple contacts

0DHex

Memo

Sequential Function Chart

STL

Sequential Function Chart SFC

Step Ladder Instruction STL, RET

RET

Features

SFC

Operation of STL Program

S21 S22 S23

Actions of Step Points

STL Transition

Repeated Usage of Output Coil

SET Sn

Repeated usage of timer

Transfer of Step Points

OUT Sn

Restrictions on Using Certain Instructions

S24 OUT

LD/LDI/LDP/LDF AND/ANI/ANDP/ANDF ANB/ORB

OR/ORI/ORP/ORF MPS/MRD/MPP INV/OUT/SET/RST

MC/MCR

Points to Note for Designing a Step Ladder Program

S41 S42 S43

Device Description

SFC diagram

Types of Sequences

S21 S42 S43

S20 S21 S22 S23 S24

S40 S41 S42 S50

Step Ladder Diagram SFC Diagram

Example of alternative divergence & alternative convergence

Step Ladder Diagram

S20 Y0 S30 S31 S32 S40 S41 S42 S50

S40

S20 S30 S31 S32 S40 S41

Restrictions on Divergence Sequence

S20 S30 S31 S32

IST Instruction

IST

Initial State

Sensor

SET

X35

S70 S80 Y3

RST

Memo

Troubleshooting

Common Problems and Solutions

Error LED is

Flashing

Troubleshooting

Error code Table Hex

Error code Description Action

Select programming

Device D1067 Description Error Code

Error Detection Devices

Error Check Description Drop Latch

Stop Æ RUN RUN Æ Stop

CANopen Function and Operation

Sint Usint Byte

Introduction of CANopen

Storage Data type

INT Uint Word

Installation and the Network Topology

Lint Ulint Lreal Lword

¾ The can signal and the data frame format

CAN+ CAN-H Can CAN-L

¾ The can network endpoint and the topology structure

¾ The topology structure of the CANopen network

Maximum

Transmission rate

Bit/second

Communication

TAP-CN01

TAP-CN02

CANopen Protocol

Introduction of the CANopen Protocol

¾ The object dictionary

CANopen Communication Object

¾ PDO process data object

Type PDO transmission

RTR

PDO1

LSB MSB

Byte Object Data Identifier ¾ SDO service data object

COB-ID

Request code Description Hex

— Module control services

Initialization Pre-operational Operational Stopped

PDO SDO Sync

Emcy

Command specifier Function Hex

— Error control services

NMT

Predefined Connection Set

— Boot-up services

— Emergency object

Object Function code

PLC device Mapping area Mapping length

Data Structure of SDO Request Message

PLC device Request message High byte Low byte

PLC device Response message High byte Low byte

Status code Explanation

0B~FF

PLC device Request message High byteHex Low byteHex

PLC device Response message High byteHex Low byteHex

NMT service code Hex Function

Data Structure of NMT Message

Example 1 Stop slave of No through NMT

Data Structure of Emergency Request Message

82(hex)

DVP32ES2-C

¾ Hardware Connection

¾ Editing the Ladder Diagram through WPLsoft

Indicators and Troubleshooting

¾ RUN indicator LED indicator Description How to deal with

LED indicator Description How to deal with

CANopen Network Node State Display

Code Indication How to correct

D9989 D9990 D9991 D9992 D9993 D9994 D9995 D9996 Register

Code Indication How to correct

Application Example

¾ Setting Servo Parameters

Parameter Setting Explanation

¾ Hareware Connection

¾ Setting CANopen Baud Rate and Node ID of DVP-ES2-C

Explanation Default

DVP-ES2-C

Explanation Default

¾ Node Configuration

¾ Network Scanning

Page

Transmission Type Description Remark

Synch

Asynch

Program explanation

DVPES2C

Object Dictionary

COB-ID Sync

COB-ID Emcy

Index Subindex Object name Data type Attribute Default value

Index Subindex Object name Data type Attribute Default value

Index Subindex Object name Data type Attribute

Index Subindex Object name Data type Attribute Default value

Index Subindex Object name Data type Attribute Default value

Index Subindex Object name Data type Attribute Default value

Index Subindex Object name Data type Attribute Default value

An introduction of installing the USB driver in the PLC

Appendix

Installing the USB Driver

Installing the driver

Appedndix a