~

ex>

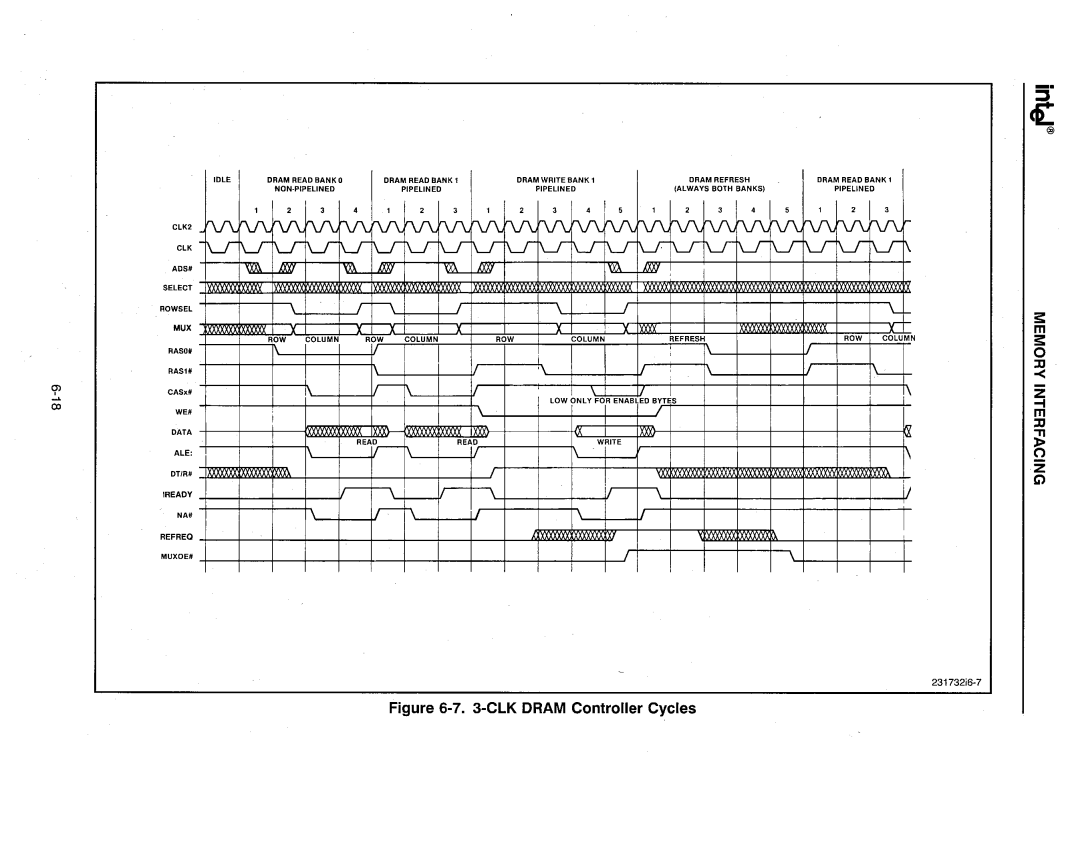

IDLE | DRAM READ BANK 0 | I DRAM READ BANK 1 |

| DRAM WRITE BANK 1 |

| DRAM REFRESH | DRAM READ BANK 1 | |||

| NON·PIPEUNED |

|

| PIPEUNED |

|

| PIPELINED |

| (ALWAYS BOTH BANKS) | PIPELINED |

| 1234123 | 1 | 2 3 4 | I 5 | 1 2 3 4 | 5 | ||||

ClK2 ~~JV\I\.~[v\.'V\.~~'V\. | ||||||||||

ClK Y Y \J"Y | ~\J"Y Y | \J" \J" \J"Y | V | Y V \J" \J"[\ | ||||||

ADS. | W>L ...J1iU | W |

|

|

| ~ ~! |

| |||

SELECT |

|

|

|

|

|

|

|

|

|

|

ROWSEl |

| r | ~ |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

MUX |

| X |

|

| X |

|

|

|

| X |

| ROW COLUMN |

| ROW | COLUMN |

| ROW | COLUMN | REFRESH | ROW CQlUMP | |

RASO' |

|

|

|

|

|

|

|

| I | |

RAS1' |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

CASd | , |

| ' - 1\ |

|

| lOW ONLY 'ForlEDBYTJS | ,\ | |||

|

|

|

|

|

|

| ||||

WEO |

|

|

|

|

|

|

|

|

| |

I |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

DATA |

|

|

|

|

|

|

|

|

|

|

|

| READ |

| WRITE |

|

| ||||

ALE: |

|

|

|

|

|

| \ | |||

|

|

|

|

|

|

|

|

| ||

DT/R. |

|

|

|

|

|

|

|

|

|

|

IREADY |

| r |

|

|

|

|

|

| J | |

|

|

|

|

|

|

|

|

| ||

NAO |

|

| ~1"\ |

|

|

|

|

| I | |

|

|

|

|

|

|

|

|

|

| |

REFRED

MUXOE' | '- |

| I |

l

<8

!: m

!:

o

::D

Z

~

Z

G)