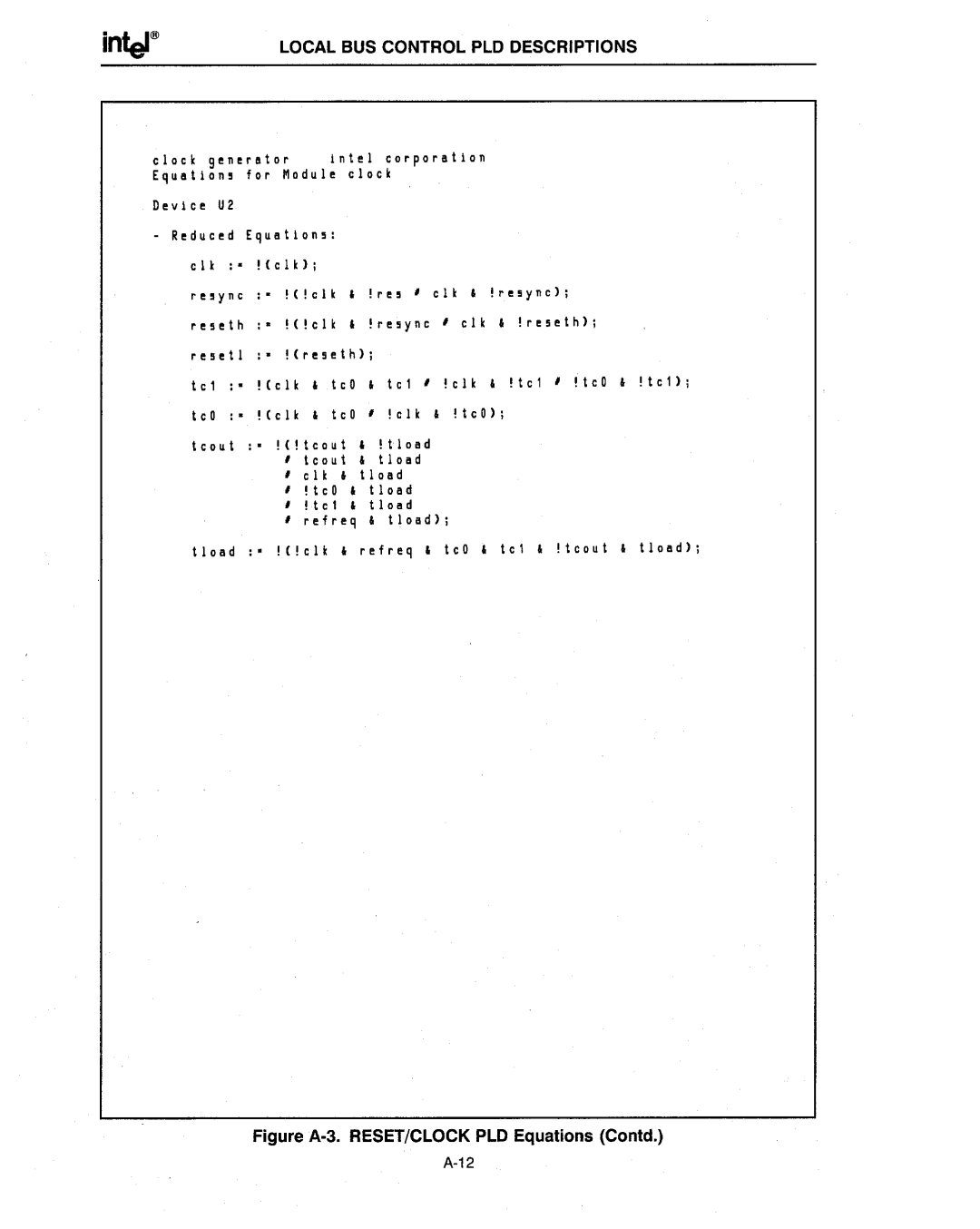

LOCAL BUS CONTROL PLD DESCRIPTIONS

clock generator Intel corporation Equation' for Module clock

Device U2

-Reduced Equation': clk :- !(elk);

re,yne :- !(!elk • Ire, , elk • !resync);

reseth .- !(!elk !re5Ync' elk 6 !reseth); re,etl .- !(re,eth);

tel :- !lelk teO tel' !elk , !tel , !teO , !te1);

teO :- !(elk teO' !elk , !teO);

teout :- !(!tcod , !tload

,teout 6 tload

,elk . tload

,!teO 6 tload !t e 1 , t loa d refreq'tloed);

tload .- !l!elk , refreq , teO' tel' !teout , tload);