I/O INTERFACING

82289

SO# | SO# | LLOCK# |

| ||

Sl# |

| ||||

Sl# | CBRO# | I |

| ||

|

| ||||

M/IO# | MIIO# | BUSY# | I |

| |

|

| ||||

READY# | READY# | BPRO# | 80286 | ||

MBEN | |||||

SYSB | BREQ# | I | COMPATIBLE | ||

LOCK# | BUS | ||||

LOCK# |

|

|

| ||

| AEN# | I- |

| ||

| BPRN# |

| |||

|

|

|

|

82288

| ' | SOH | MRDC# | |

| Sl# | MWDC# | ||

|

| MIIO# | 10RC# | |

|

| READY# | 10WC# | |

|

| CENL | INTA# | |

1 |

| MB | ALE | TO ADDRESS LATCH |

|

| |||

| CMDLY |

|

| |

~ | l | AEN# | DT/R# | TO DATA TRANSCEIVER |

| DEN | TO DATA TRANSCEIVER | ||

|

|

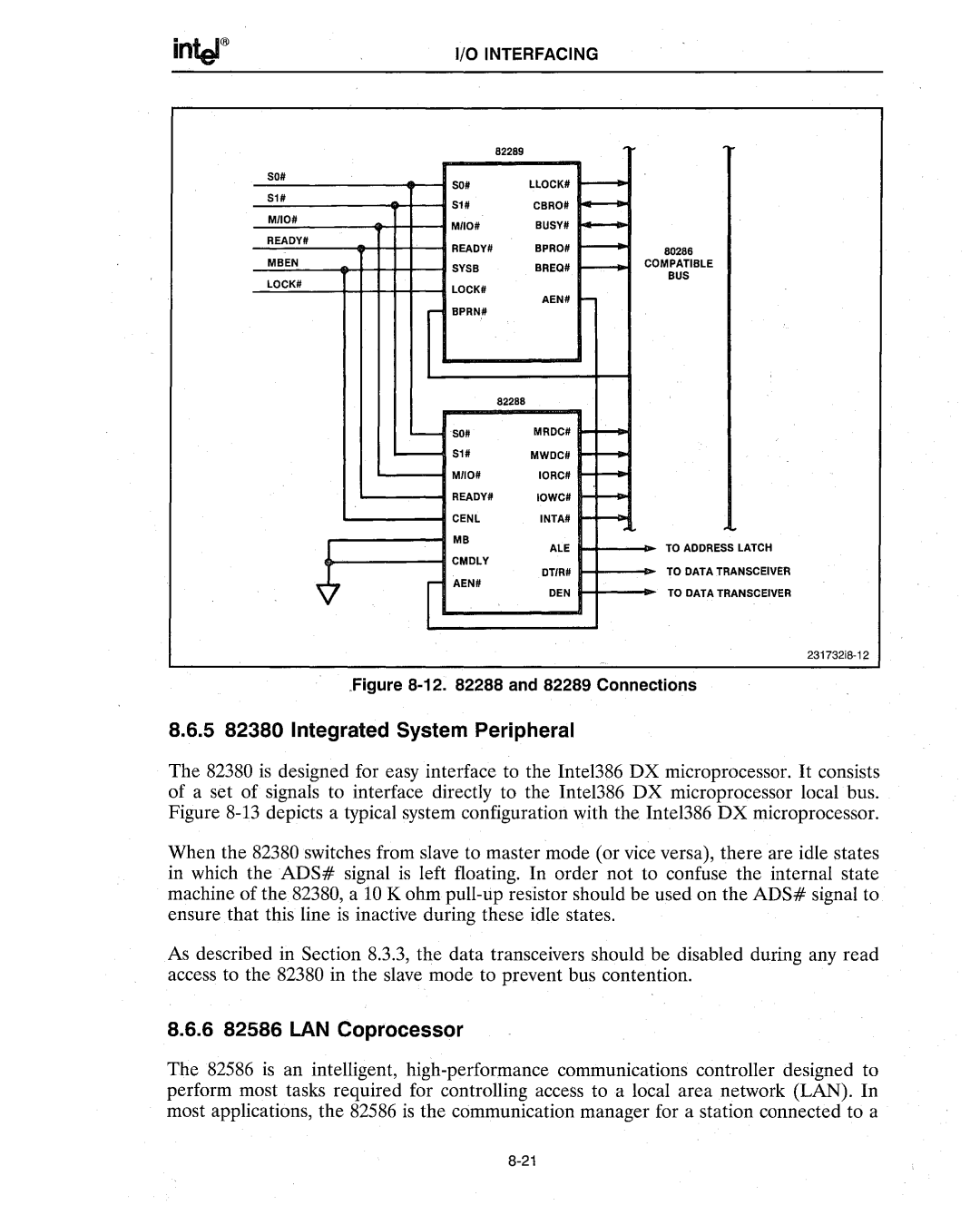

,Figure 8-12. 82288 and 82289 Connections

8.6.5 82380 Integrated System Peripheral

The 82380 is designed for easy interface to the Intel386 DX microprocessor. It consists of a set of signals to interface directly to the Intel386 DX microprocessor local bus. Figure

When the 82380 switches from slave to master mode (or vice versa), there are idle states in which the ADS# signal is left floating. In order not to confuse the internal state machine of the 82380, a 10 K ohm

As described in Section 8.3.3, the data transceivers should be disabled during any read access to the 82380 in the slave mode to prevent bus contention.

8.6.6 82586 LAN Coprocessor

The 82586 is an intelligent,