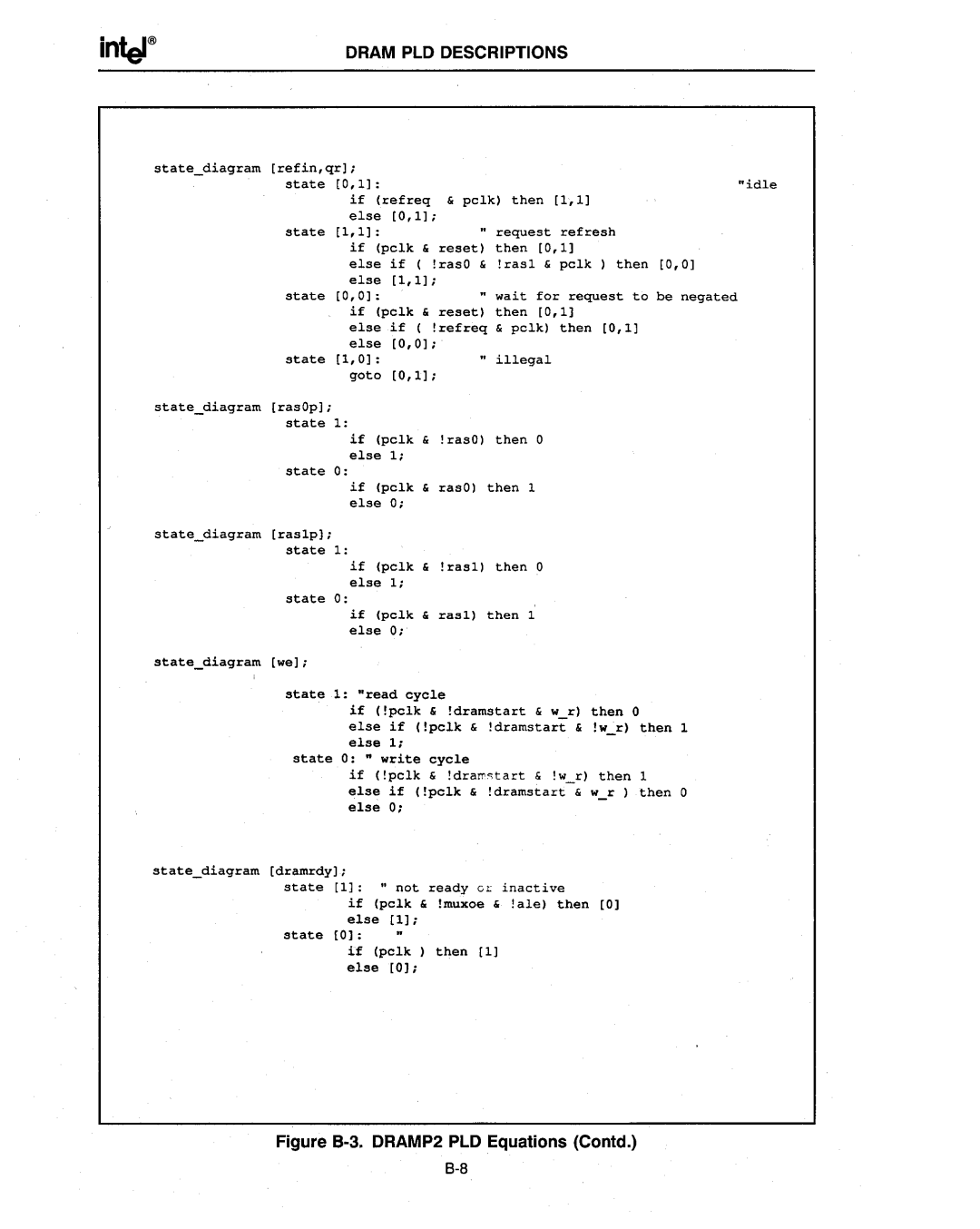

DRAM PLD DESCRIPTIONS

state_diagram [refin,qr]; |

| |

state | [0,1]: | "idle |

| if (refreq & pclk) then [1,1] | |

| else | [0,1]; |

state | [1,1]: | " request refresh |

| if (pclk & reset) then [0,1] | |

| else if ( !rasO & !rasl & pclk ) then [0,0] | |

| else | [1,1]; |

state | [0,0]: | " wait for request to be negated |

| if (pclk & reset) then [0,1] | |

| else if ( !refreq & pclk) then [0,1] | |

| else | [0,0]; |

state | [1,0]: | " illegal |

| goto | [0,1]; |

state_diagram [rasOp]; state 1:

if (pclk & !rasO) then 0 else 1;

state 0:

if (pclk & rasO) then 1 else 0;

state_diagram [raslp]; state 1:

if (pclk & !rasl) then 0 else 1;

state 0:

if (pclk & rasl) then 1 else 0;

state_diagram [we];

state 1: "read cycle

if (!pclk & !dramstart & w_r) then 0

else if (!pclk & !dramstart & !w~r) then 1 else 1;

state 0: " write cycle

if (!pclk & !dra~~tart & !w_r) then 1

else if (!pclk & !dramstart & w_r then 0 else 0;

state_diagram [dramrdy];

state [1]: "not ready Gr inactive

if (pclk & !muxoe & !ale) then [0] else [1];

state [0]:

if (pclk ) then [1] else [0];