LOCAL BUS INTERFACE

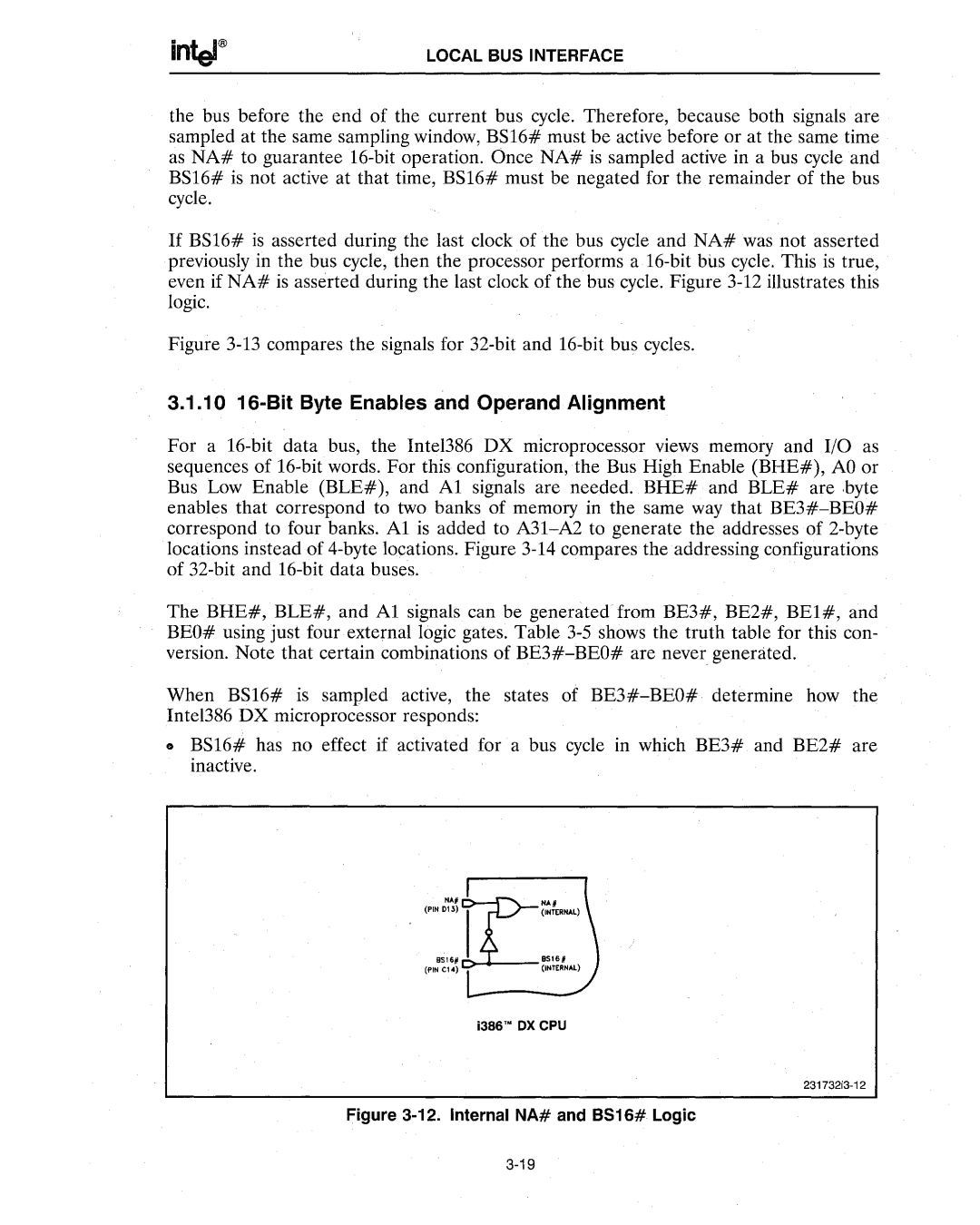

the bus before the end of the current bus cycle. Therefore, because both signals are sampled at the same sampling window, BSI6# must be active before or at the same time as NA# to guarantee

If BSI6# is asserted during the last clock of the bus cycle and NA# was not asserted previously in the bus cycle, then the processor performs a

Figure 3-13 compares the signals for 32-bit and 16-bit bus cycles.

3.1.10 i6-Bit Byte Enables and Operand Alignment

For a

The BHE#, BLE#, and Al signals can be generated from BE3#, BE2#, BEl#, and BEO# using just four external logic gates. Table

When BSI6# is sampled active, the states of

.. BSI6# has no effect if activated for a bus cycle in which BE3# and BE2# are inactive.

NAIIL1NAI | ||

(PIN 013) | I | (lNTtRNAL) |

85161 | T | BS1S, |

(PIN CI4) | ('NTERNAL) | |

-

i38S'· ox CPu