MULTIBUS II AND Intel386 DX MICROPROCESSOR

10.2.1iPSe Interface

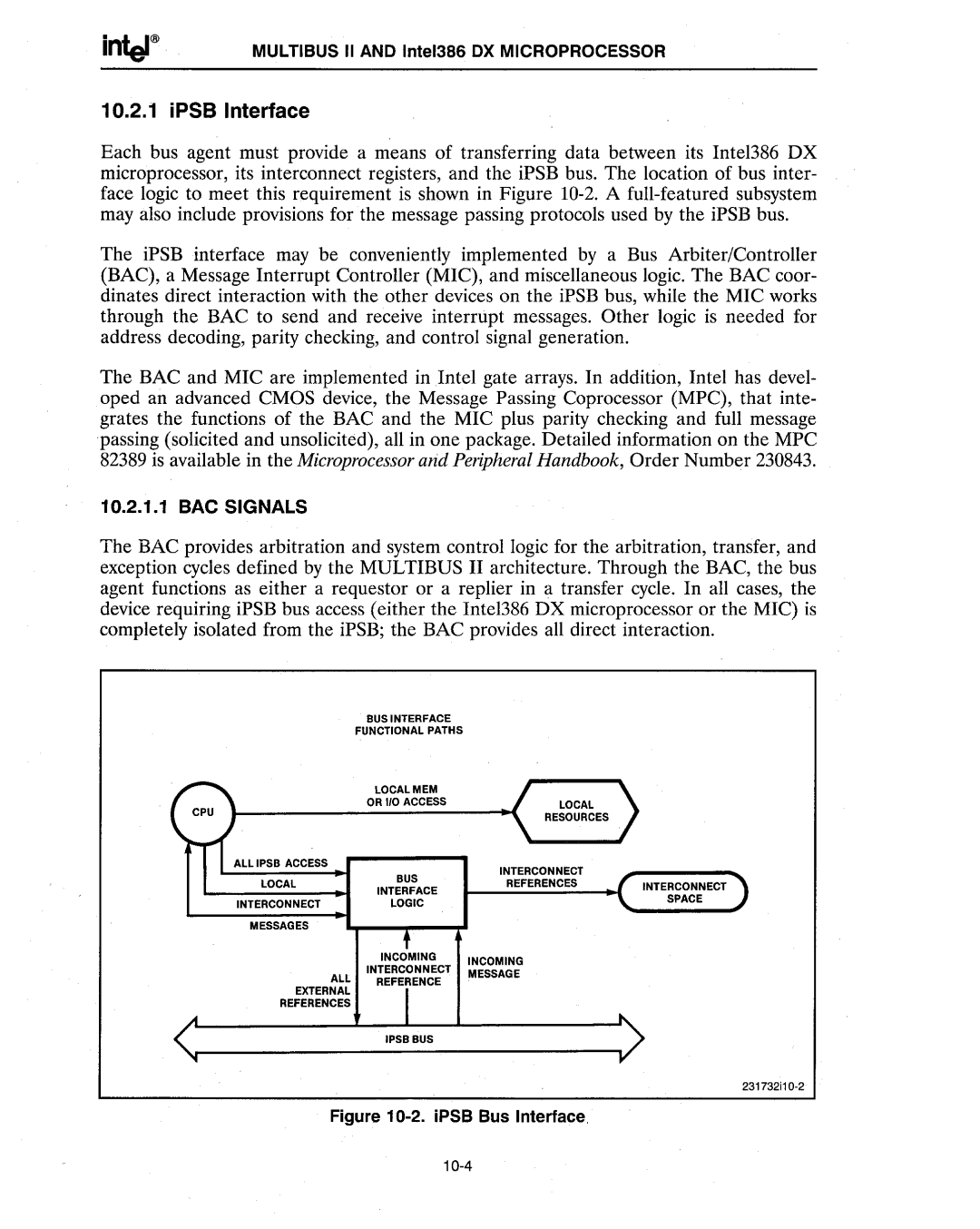

Each bus agent must provide a means of transferring data between its Intel386 DX microprocessor, its interconnect registers, and the iPSB bus. The location of bus inter- face logic to meet this requirement is shown in Figure

The iPSB interface may be conveniently implemented by a Bus Arbiter/Controller (BAC), a Message Interrupt Controller (MIC), and miscellaneous logic. The BAC coor- dinates direct interaction with the other devices on the iPSB bus, while the MIC works through the BAC to send and receive interrupt messages. Other logic is needed for address decoding, parity checking, and control signal generation.

The BAC and MIC are implemented in Intel gate arrays. In addition, Intel has devel- oped an advanced CMOS device, the Message Passing Coprocessor (MPC), that inte- grates the functions of the BAC and the MIC plus parity checking and full message passing (solicited and unsolicited), all in one package. Detailed information on the MPC 82389 is available in the Microprocessor arid Peripheral Handbook, Order Number 230843.

10.2.1.1 BAC SIGNALS

The BAC provides arbitration and system control logic for the arbitration, transfer, and exception cycles defined by the MULTIBUS II architecture. Through the BAC, the bus agent functions as either a requestor or a replier in a transfer cycle. In all cases, the device requiring iPSB bus access (either the Intel386 DX microprocessor or the MIC) is completely isolated from the iPSB; the BAC provides all direct interaction.

BUS INTERFACE

FUNCTIONAL PATHS

LOCALMEM

OR I/O ACCESS

| BUS | INTERCONN£CT |

| |

LOCAL | REFERENCES | INTERCONNECT | ||

INTERFACE | ||||

|

| SPACE | ||

INTERCONNECT | LOGIC |

| ||

|

| |||

MESSAGES |

|

|

| |

| INCOMING | INCOMING |

| |

| INTERCONNECT |

| ||

ALL | MESSAGE |

| ||

REFERENCE |

| |||

|

| |||

EXTERNAL |

|

| ||

|

|

| ||

REFERENCES |

|

|

| |

| IPSBBUS |

|

|

231732i10·2