CACHE SUBSYSTEMS

•In a power failure, the data in the cache is lost, so there is no way to tell which locations of the main memory contain stale data. Therefore, the main memory as well as the cache must be considered volatile and provisions must be made to save the data in the cache in the case ofa power failure.

7.3.4Cache Coherency

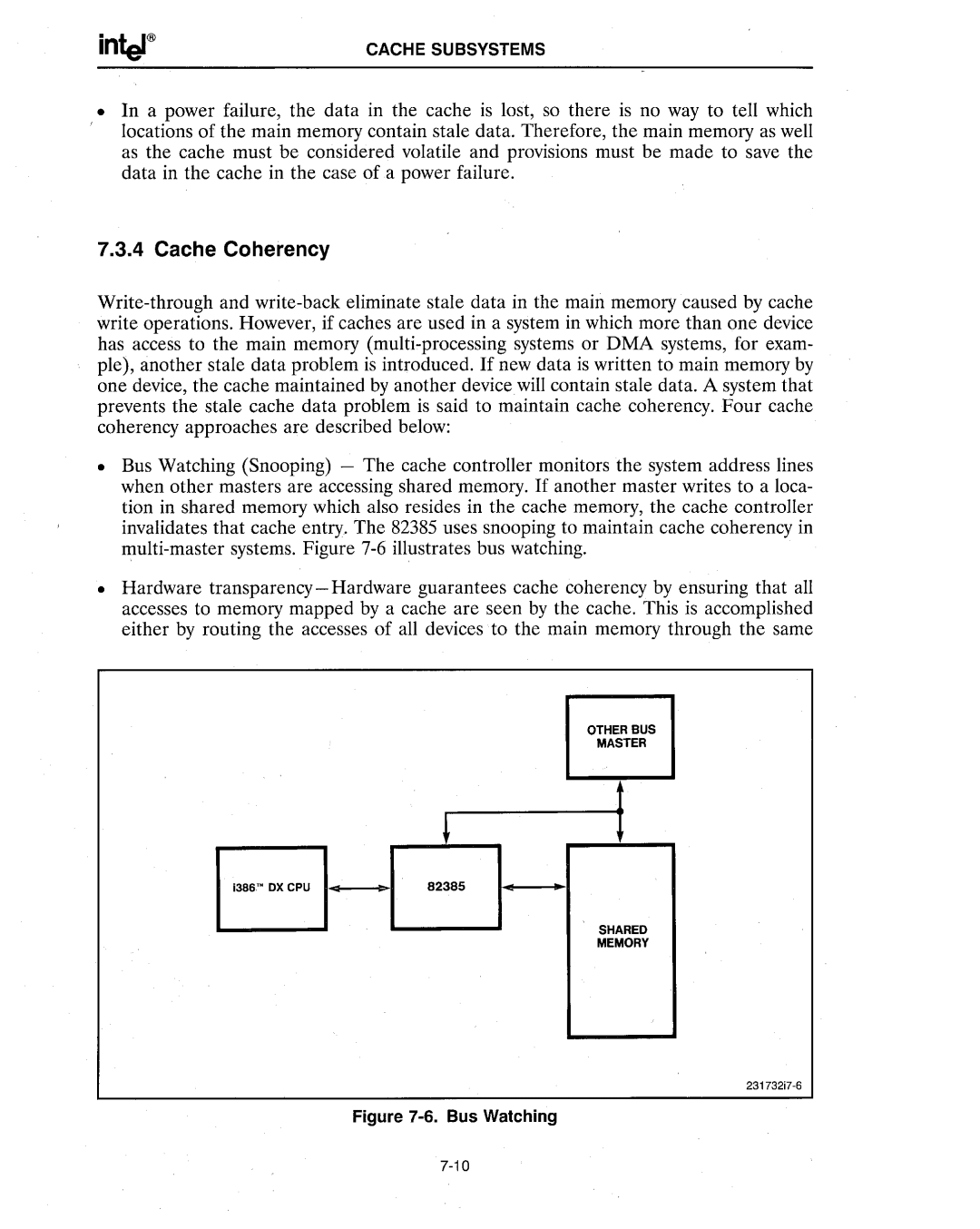

•Bus Watching (Snooping) - The cache controller monitors the system address lines when other masters are accessing shared memory. If another master writes to a loca~ tion in shared memory which also resides in the cache memory, the cache controller invalidates that cache entry. The 82385 uses snooping to maintain cache coherency in

•Hardware transparency - Hardware guarantees cache coherency by ensuring that all accesses to memory mapped by a cache are seen by the cache. This is accomplished either by routing the accesses of all devices to the main memory through the same

OTHER BUS

MASTER

|

|

| ~ |

1386'· OX CPU | • | .. | 82385 |

SHARED

MEMORY

231732i7·6