lOCAL BUS INTERFACE

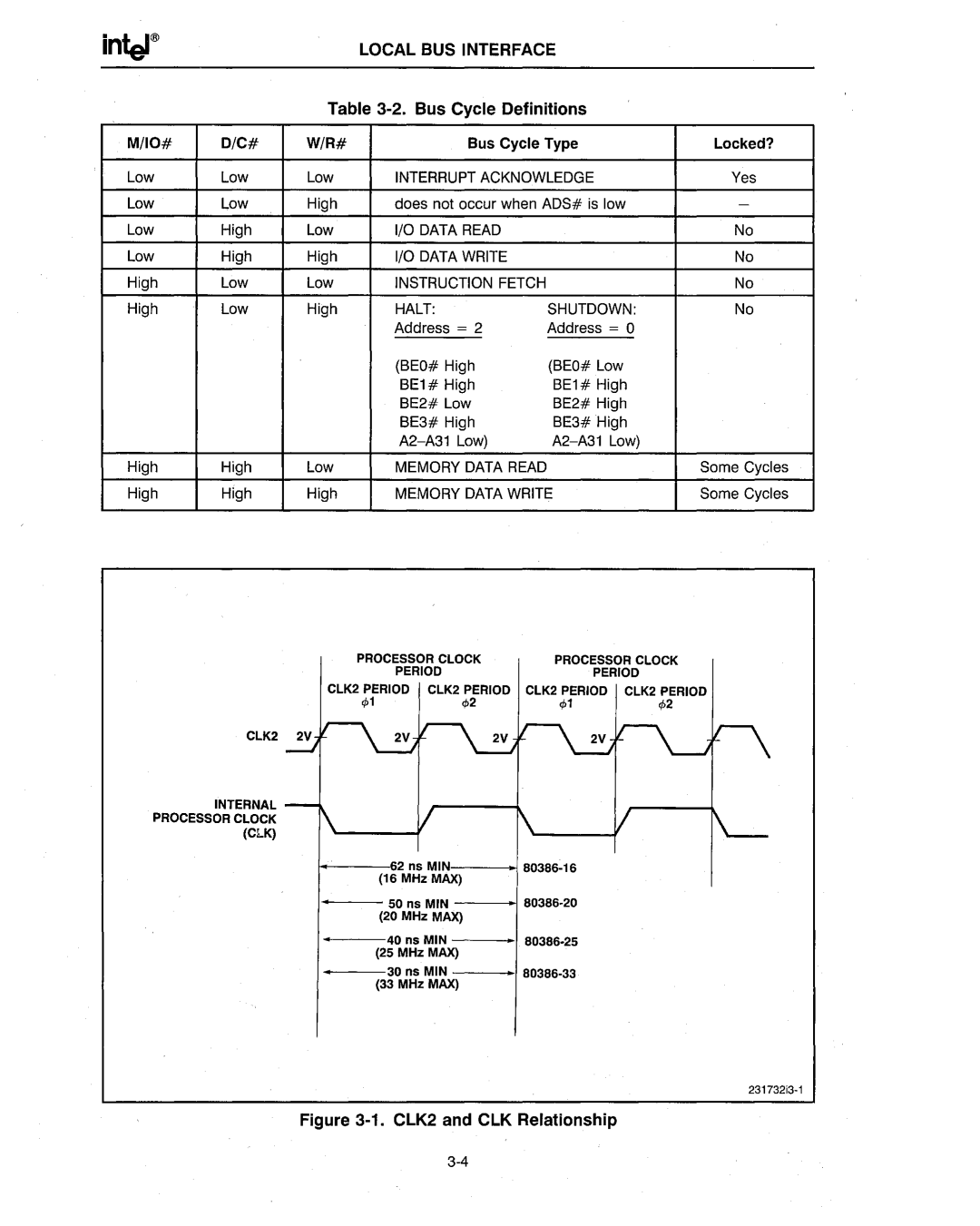

Table 3-2. Bus Cycle Definitions

M/IO# | D/C# | W/R# | Bus Cycle Type | Locked? | |

Low | Low | Low | INTERRUPT ACKNOWLEDGE | Yes | |

Low | Low | High | does not occur when ADS# is low | - | |

Low | High | Low | I/O DATA READ |

| No |

Low | High | High | I/O DATA WRITE |

| No |

High | Low | Low | INSTRUCTION FETCH |

| No |

High | Low | High | HALT: | SHUTDOWN: | No |

|

|

| Address = 2 | Address = 0 |

|

|

|

| (BEO# High | (BEO# Low |

|

|

|

| BE1# High | BE1# High |

|

|

|

| BE2# Low | BE2# High |

|

|

|

| BE3# High | BE3# High |

|

|

|

|

| ||

High | High | Low | MEMORY DATA READ |

| Some Cycles |

High | High | High | MEMORY DATA WRITE | Some Cycles | |

PROCESSOR CLOCK | PROCESSOR CLOCK | ||

| PERIOD |

| PERIOD |

CLK2 PERIOD CLK2 PERIOD CLK2 PERIOD CLK2 PERIOD | |||

<1>1 | <1>2 | <1>1 | <1>2 |

INTERNAL PROCESSOR CLOCK (CLK)

62 ns MIN | 80386·16 |

(16 MHz MAX) |

|

50 ns MIN | |

(20 MHz MAX) | · |

40 ns MIN | |

(25 MHz MAX) | · |

30 ns MIN | |

(33 MHz MAX) | · |