LOCAL BUS INTERFACE

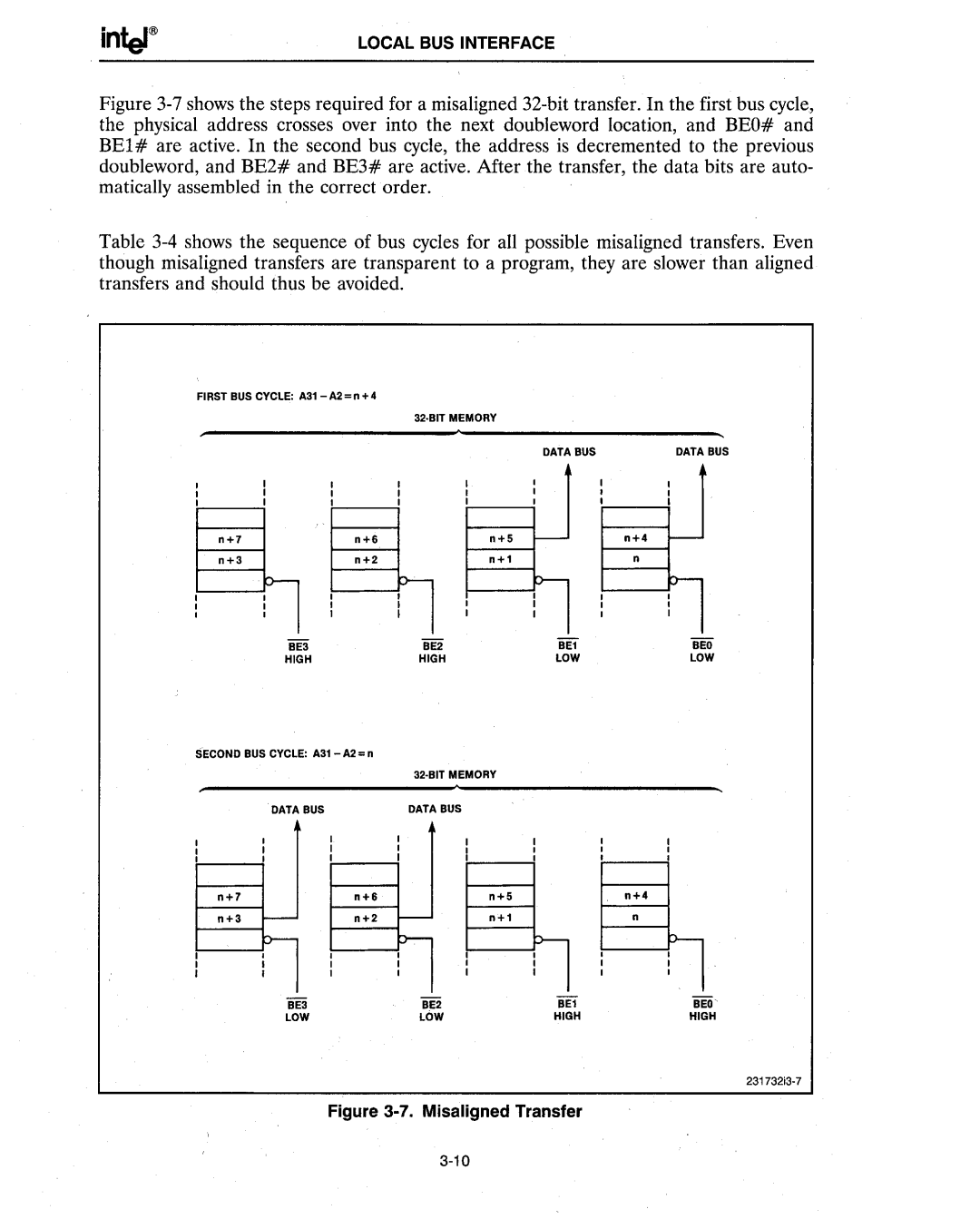

Figure 3-7 shows the steps required for a misaligned 32-bit transfer. In the first bus cycle, the physical address crosses over into the next doubleword location, and BEO# and BEl # are active. In the second bus cycle, the address is decremented to the previous doubleword, and BE2# and BE3# are active. After the transfer, the data bits are auto- matically assembled in the correct order.

Table 3-4 shows the sequence of bus cycles for all possible misaligned· transfers. Even though misaligned transfers are transparent to a program, they are slower than aligned transfers and should thus be avoided.

FIRST BUS CYCLE: A31 - A2 = n +4

32·BITMEMORY

DATA BUS | DATA BUS |

n+7 | n+6 | n+5 | n+4 |

n+3 |

|

|

|

BE3 | BE2 | BE1 | BEO |

HIGH | HIGH | LOW | LOW |

SECOND BUS CYCLE: A31 - A2 = n

| 32·BITMEMORY |

DATA BUS | DATA BUS |

n+7 | n+8 | n+5 | n+4 |

n+3 |

|

|

|

iE3 | BE2 | BE1 | BEO' |

LOW | LOW | HIGH | HIGH |