I/O INTERFACING

For a cascaded interrupt request, the 82380 PIC will output an

Chapter 9 describes the interface to slave controllers that reside on a MULTIBUS I system bus.

8.5.3 8259A Interrupt Controller

The 8259A Programmable Interrupt Controller is designed for use in

The 8259A handles interrupt priority resolution and returns a preprogrammed service routine vector to the InteI386 DX microprocessor during an

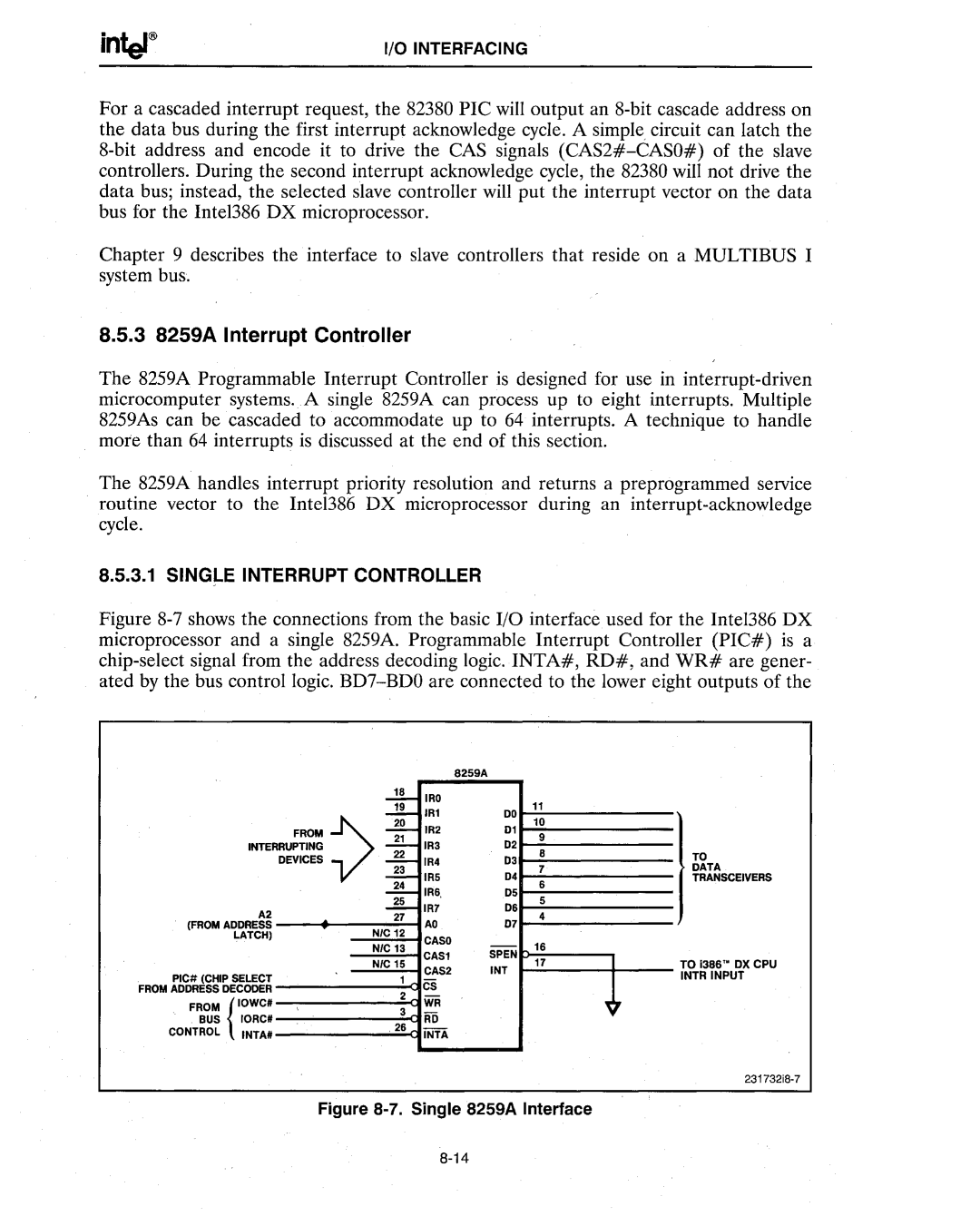

8.5.3.1 SINGLE INTERRUPT CONTROLLER

Figure 8-7 shows the connections from the basic I/O interfaceused for the InteI386 DX microprocessor and a single 8259A. Programmable Interrupt Controller (PIC#) is a chip-select signal from the address decoding logic. INTA#, RD#, and WR# are gener- ated by the bus control logic. BD7-BDO are connected to the lower eight outputs of the

|

|

|

| 8259A |

|

|

|

| ~ IRO |

| 11 |

| |

|

|

| IRl | DO |

| |

|

|

| 10 |

| ||

|

|

| IR2 | 01 |

| |

| FROM |

| 9 |

| ||

| 02 |

| ||||

| INTERRUPTING |

|

| |||

| DEVICES | 03 | 8 | TO | ||

| 7 | DATA | ||||

|

|

| 04 | 6 | TRANSCEIVERS | |

|

| ~ IR6, | 05 | 5 | I | |

|

| 2L IR7 | 06 | |||

| A2 | 4 | ||||

| 27 | AO | 07 | |||

(FROM ADDRESS | N/C 12 |

|

| |||

| LATCH) |

| - |

|

| |

|

| NIC 13 CASO | 16 |

| ||

|

| N/C15 | CASl | SPEN | 17 | TO ;386'·ox CPU |

|

| CAS2 | INT | |||

PIC# (CHIP SELECT | 1 |

| INTR INPUT | |||

Cs |

|

| ||||

FROM ADDRESS DECODER | 2 |

|

|

| ||

|

| WR |

|

| ~7 | |

FROM {'OWC# | 3 |

|

| |||

AD |

|

| ||||

BUS | IORC# | 26 |

|

|

| |

CONTROL | INTA# | INTA |

|

|

| |

|

|

|

| |||

231732i8·7