I/O INTERFACING

|

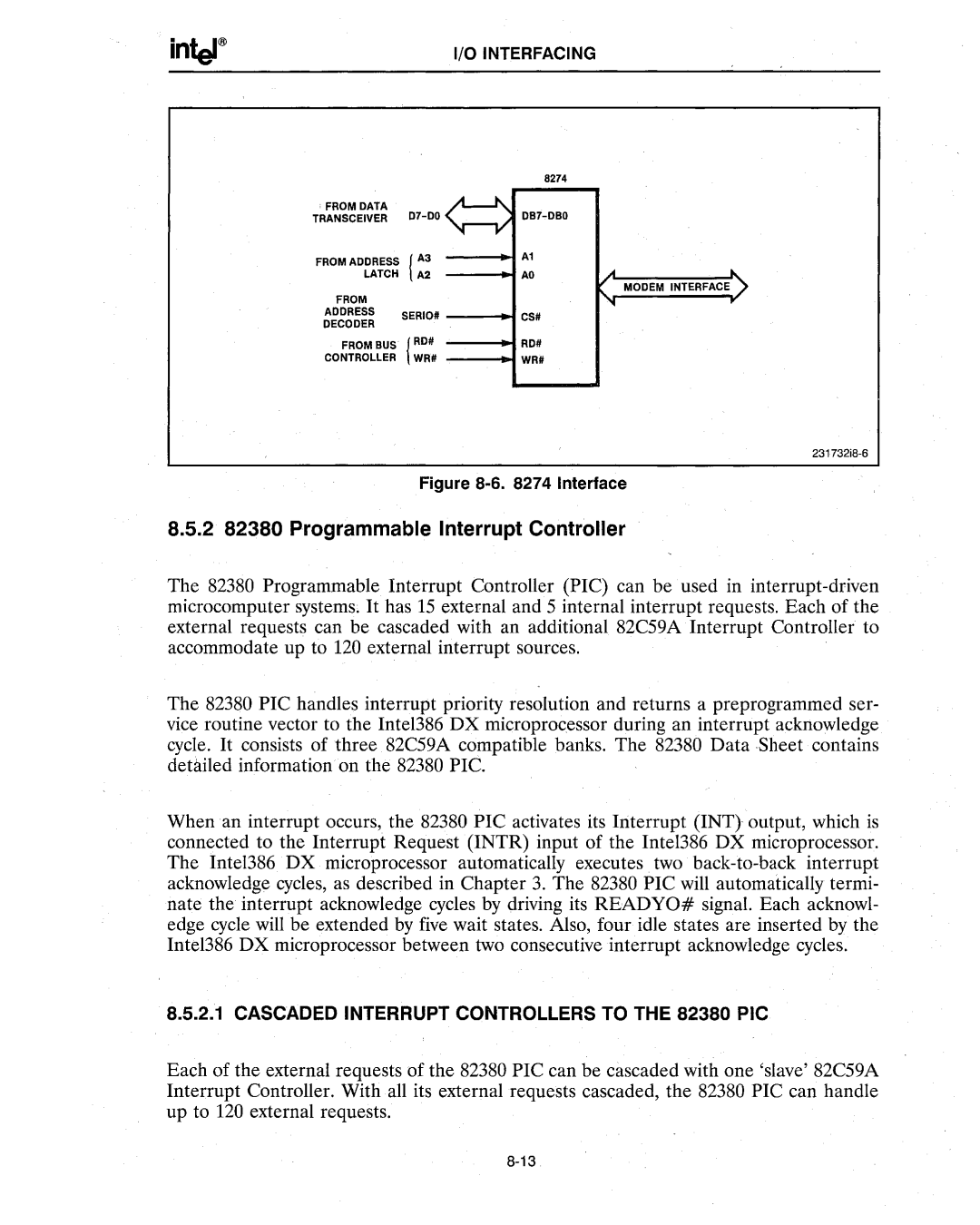

| 8274 | |

FROM DATA | |||

TRANSCEIVER | |||

FROM ADDRESS | (A3 | Al | |

| |||

LATCH | A2 | AO | |

|

| MODEM INTERFACE | |

FROM |

|

| |

ADDRESS | SERIO# | CS# | |

DECODER | |||

|

| ||

FROM BUS | (RDN | RDN | |

CONTROLLER | WRN | WRH |

Figure 8-6. 8274 Interface

8.5.2 82380 Programmable Interrupt Controller

The 82380 Programmable Interrupt Controller (PIC) can be used in

The 82380 PIC handles interrupt priority resolution and returns a preprogrammed ser- vice routine vector to the Intel386 DX microprocessor during an interrupt acknowledge cycle. It consists of three 82C59A compatible banks. The 82380 Data Sheet contains detailed information on the 82380 PIC.

When an interrupt occurs, the 82380 PIC activates its Interrupt (INT) output, which is connected to the Interrupt Request (INTR) input of the Inte1386 DX microprocessor. The Intel386 DX microprocessor automatically executes two

8.5.2.1 CASCADED INTERRUPT CONTROLLERS TO THE 82380 PIC

Each of the external requests of the 82380 PIC can be cascaded with one 'slave' 82C59A Interrupt Controller. With all its external requests cascaded, the 82380 PIC can handle up to 120 external requests.