LOCAL BUS INTERFACE

ALWAYS

READY# ASSERTED·

REQUEST PENDING

READY# NEGATED·

NA# NEGATED

BUB States:

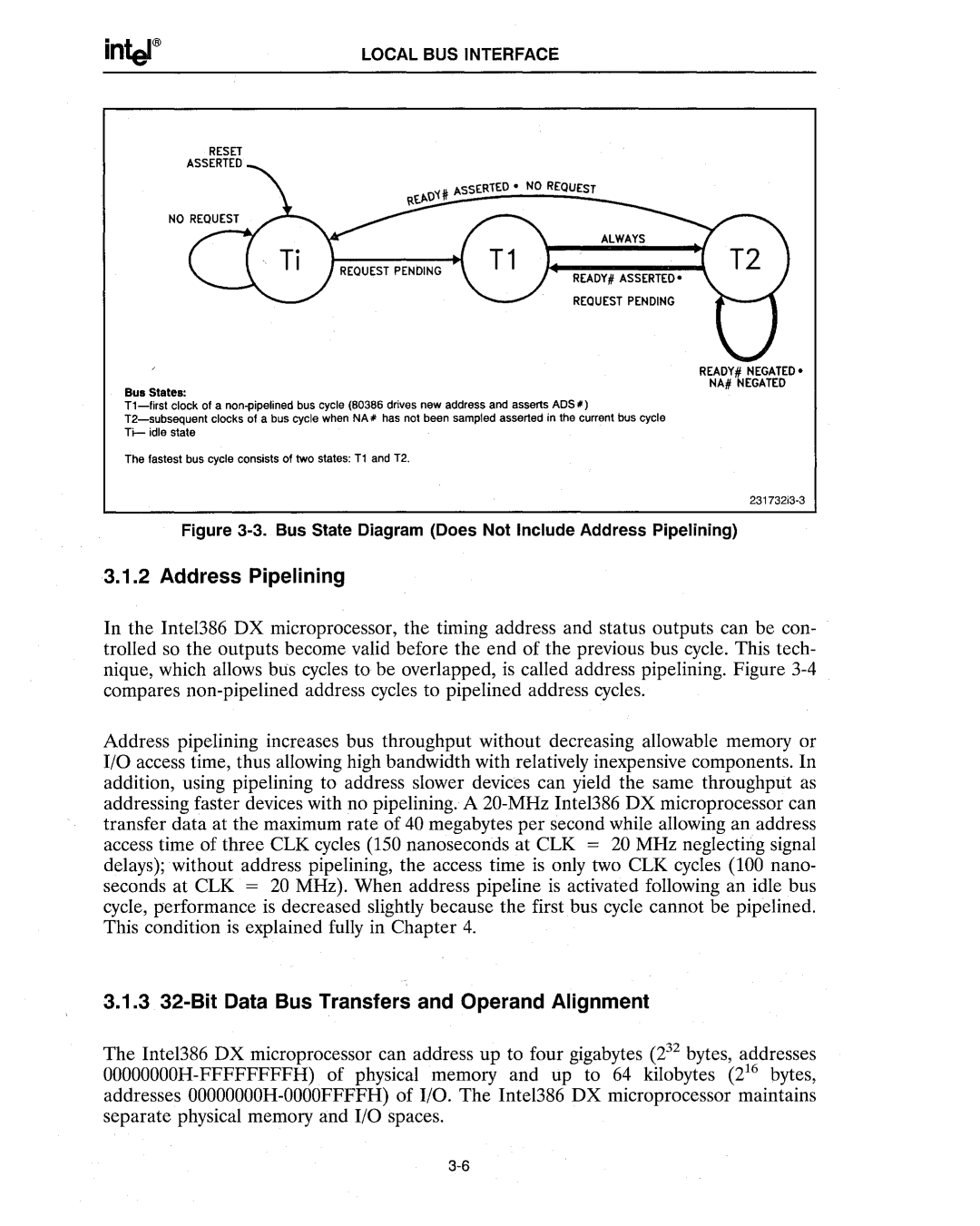

The fastest bus cycle consists of two states: T1 and T2.

Figure 3-3. Bus State Diagram (Does Not Include Address Pipelining)

3.1.2 Address Pipelining

In the Intel386 OX microprocessor, the timing address and status outputs can be con- trolled so the outputs become valid before the end of the previous bus cycle_ This tech- nique, which allows bus cycles to be overlapped, is called address pipelining. Figure

Address pipelining increases bus throughput without decreasing allowable memory or I/O access time, thus allowing high bandwidth with relatively inexpensive components. In addition, using pipelining to address slower devices can yield the same throughput as addressing faster devices with no pipelining. A

3.1.3 32-Bit Data Bus Transfers and Operand Alignment

The Inte1386 OX microprocessor can address up to four gigabytes (232 bytes, addresses