CACHE SUBSYSTEMS

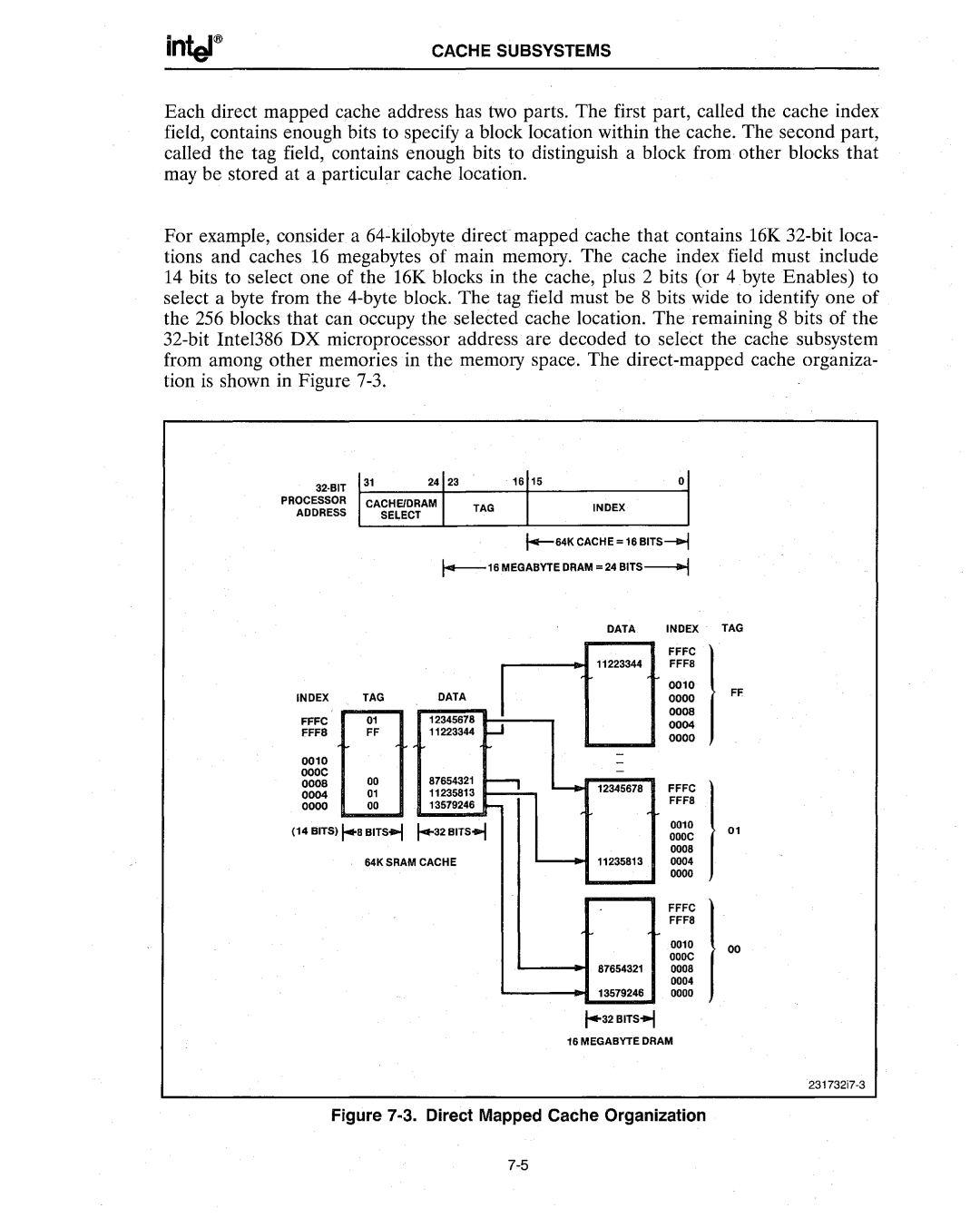

Each direct mapped Cilche address has two parts. The first part, called the cache index field, contains enough bits to specify a block location within the cache. The second part, called the tag field, contains enough bits to distinguish a block from other blocks that

.may be stored at a particular cache location.

For example, consider a

32.BIT | 131 |

| 24123 | . 16 | 15 |

|

| o |

|

PROCESSOR | ICACHE/DRAM I |

|

| INDEX |

|

| |||

ADDRESS | SE~ECT | TAG |

|

|

|

|

| ||

|

|

|

|

|

| ||||

|

|

|

| ||||||

|

|

|

|

|

|

| DATA | INDEX | TAG |

|

|

|

|

|

|

|

| FFFC |

|

|

|

|

|

|

|

| 11223344 | FFF8 |

|

INDEX | TAG |

| DATA |

|

|

|

| 0010 | FF |

|

|

|

|

| 0000 | ||||

|

|

|

|

| I | ||||

FFFC | 01 |

| 12345678 |

|

|

|

| 0008 | |

| f...J |

|

|

| 0004 | ||||

FFF8 | FF |

| 11223344 |

|

|

| |||

|

|

| 0000 | ||||||

0010 |

|

|

|

|

|

|

| ||

OOOC |

|

| 87654321 | P |

|

| - |

| I |

0008 | 00 |

| 12345678 | FFFC | |||||

0004 | 01 |

| 11235813 | ||||||

|

| FFF8 | |||||||

0000 | 00 |

| 13579246 | I- | - |

|

|

| |

|

|

|

|

|

| ||||

(14 BITS) j.8 BIT~ | j+32BITS~ |

|

|

| 0010 | 01 | |||

|

|

| OOOC | ||||||

|

|

|

|

|

|

|

| 0008 | I~ |

| 64KSRAM CACHE |

|

|

| 11235813 | 0004 | |||

|

|

|

|

|

|

|

| 0000 | |

|

|

|

|

|

|

|

| FFFC | |

|

|

|

|

|

|

|

| FFF8 | |

|

|

|

|

|

|

|

| .0010 | |

|

|

|

|

|

|

|

| OOOC | |

|

|

|

|

|

|

| 87654321 | 0008 | |

|

|

|

|

|

|

|

| 0004 | |

|

|

|

|

|

|

| 13579246 | 0000 | |

j+32BITS.j

16 MEGABYTE DRAM

231732;7·3