LOCAL BUS INTERFACE

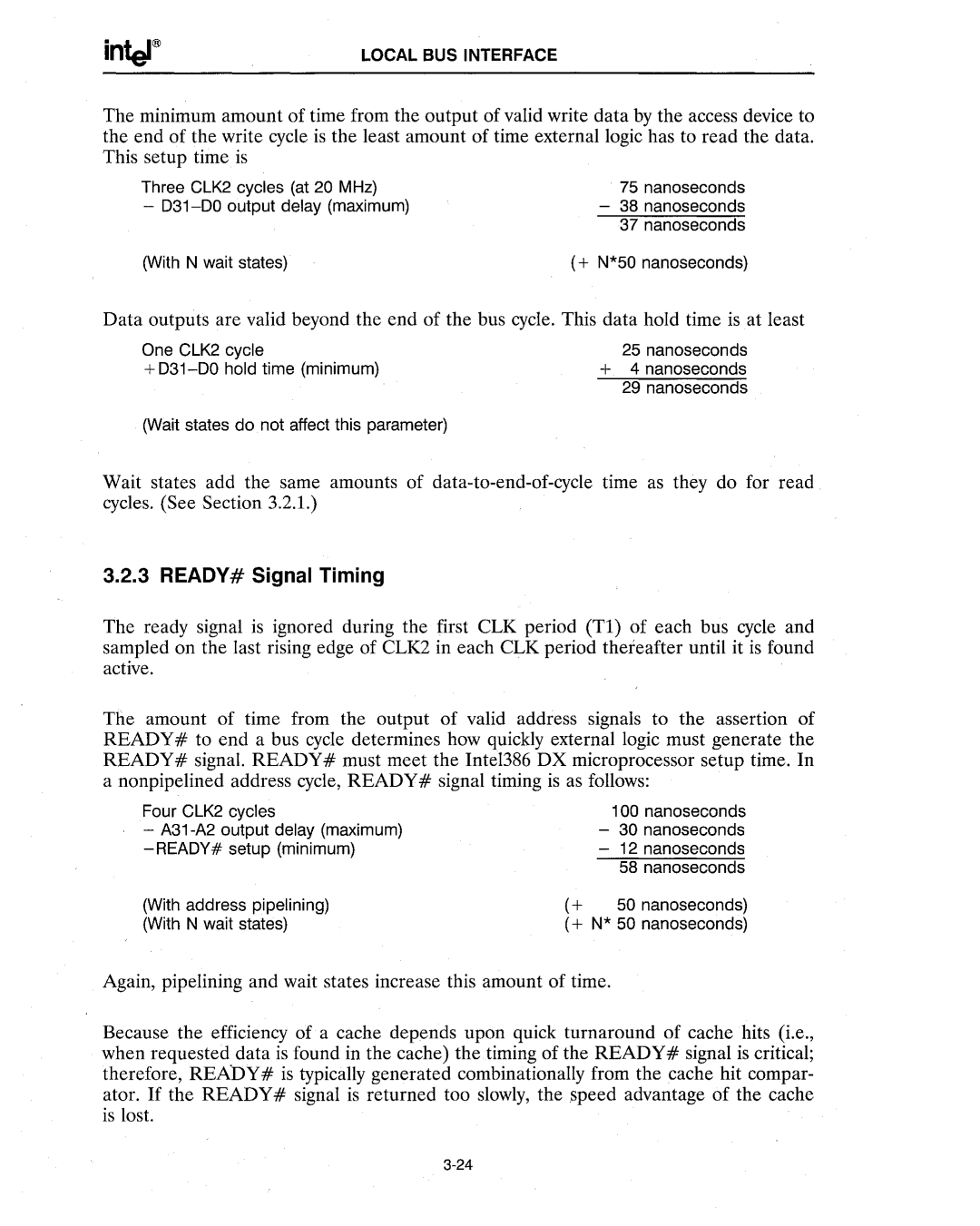

The minimum amount of time from the output of valid write data by the access device to the end of the write cycle is the least amount of time external logic has to read the data. This setup time is

Three CLK2 cycles (at 20 MHz) | 75 | nanoseconds |

- | - 38 | nanoseconds |

| 37 nanoseconds | |

(With N wait states) | (+ N*50 nanoseconds) | |

Data outputs are valid beyond the end of the bus cycle. This data hold time is at least

One CLK2 cycle | 25 nanoseconds |

+ 4 nanoseconds | |

| 29 nanoseconds |

(Wait states do. not affect this parameter) |

|

Wait states add the same amounts of

3.2.3 READY# Signal Timing

The ready signal is ignored during the first CLK period (Tl) of each bus cycle and sampled on the last rising edge of CLK2 in each CLK period thereafter until it is found active.

The amount of time from the output of valid address signals to the assertion of READY# to end a bus cycle determines how quickly external logic must generate the READY# signal. READY# must meet the Inte1386 DX microprocessor setup time. In a nonpipelined address cycle, READY# signal timing is as follows:

Four CLK2 cycles |

| 100 nanoseconds | |

- | - | 30 nanoseconds | |

- | 12 nanoseconds | ||

|

| 58 nanoseconds | |

(With address pipelining) | (+ | 50 | nanoseconds) |

(With N wait states) | (+ N* 50 | nanoseconds) | |

Again, pipelining and wait states increase this amount of time.

Because the efficiency of a cache depends upon quick turnaround of cache hits (i.e., when requested data is found in the cache) the timing of the READY# signal is critical; therefore, READY# is typically generated combinationally from the cache hit compar- ator. If the READY# signal is returned too slowly, the speed advantage of the cache is lost.