CACHE SUBSYSTEMS

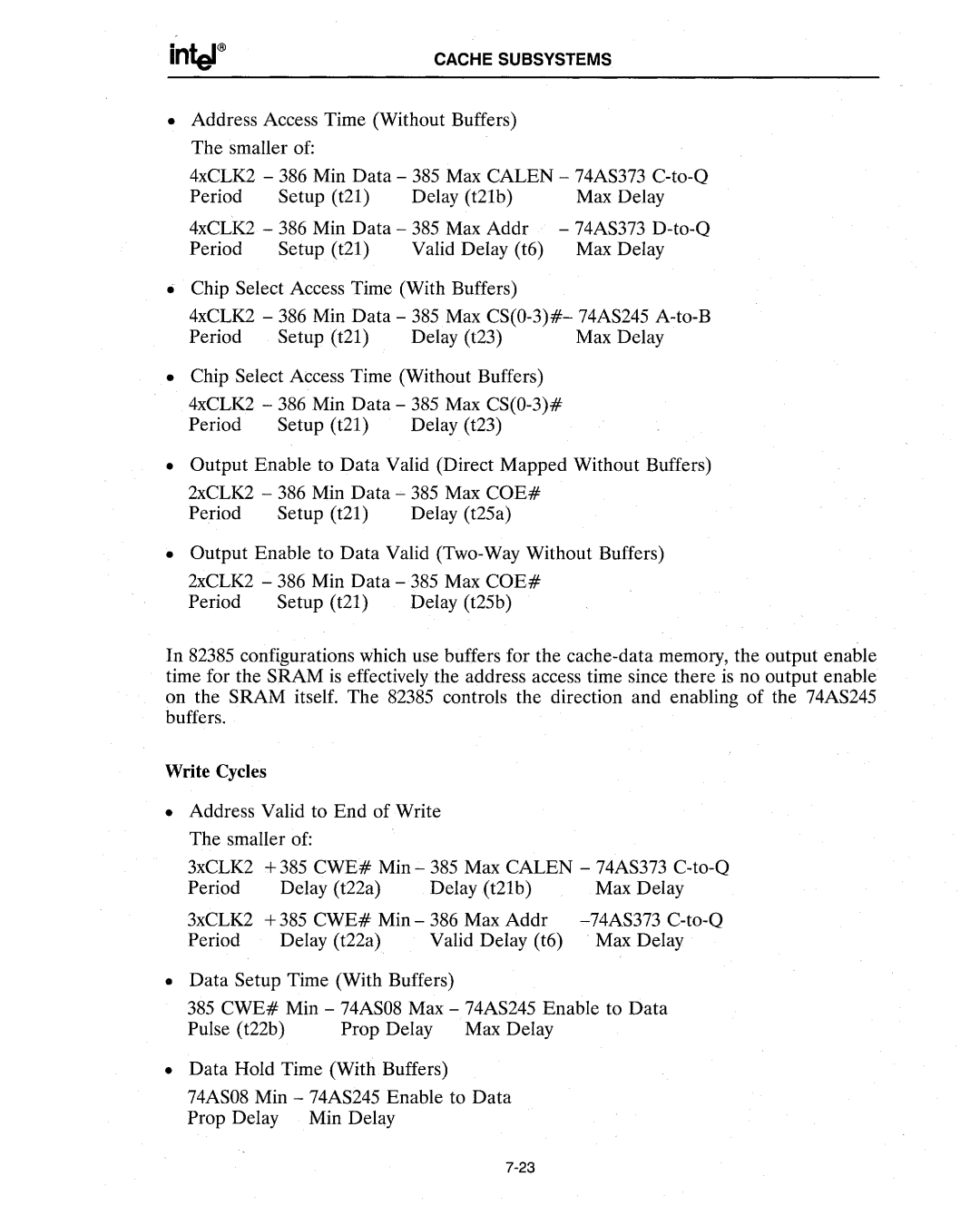

•Address Access Time (Without Buffers) The smaller of:

4xCLK2 - 386 Min Data - 385 Max CALEN - 74AS373

Period | Setup (t21) | Delay (t21b) | Max Delay |

4xCLK2 - 386 Min Data - 385 Max Addr | - 74AS373 | ||

Period | Setup (t21) | Valid Delay (t6) | Max Delay |

• Chip Select Access Time (With Buffers)

4xCLK2 - 386 Min Data - 385 Max

Period | Setup (t21) | Delay (t23) | Max Delay |

• Chip Select Access Time (Without Buffers)

4xCLK2 - 386 Min Data - 385 Max

Period Setup (t21) Delay (t23)

• Output Enable to Data Valid (Direct Mapped Without Buffers)

2xCLK2 - 386 Min Data - 385 Max COE#

Period Setup (t21) Delay (t25a)

•Output Enable to Data Valid

2xCLK2 - 386 Min Data - 385 Max COE#

Period Setup (t21) Delay (t25b)

In 82385 configurations which use buffers for the

Write Cycles

•Address Valid to End of Write The smaller of:

3xCLK2 +385 CWE# Min- 385 Max CALEN

Period | Delay (t22a) | Delay (t21b) | Max Delay |

3xCLK2 + 385 CWE# Min - 386 Max Addr

Period Delay (t22a) Valid Delay (t6) Max Delay

• Data Setup Time (With Buffers)

385 CWE# Min - 74AS08 Max - 74AS245 Enable to Data

Pulse (t22b) Prop Delay Max Delay

• Data Hold Time (With Buffers)

74AS08 Min - 74AS245 Enable to Data

Prop Delay Min Delay