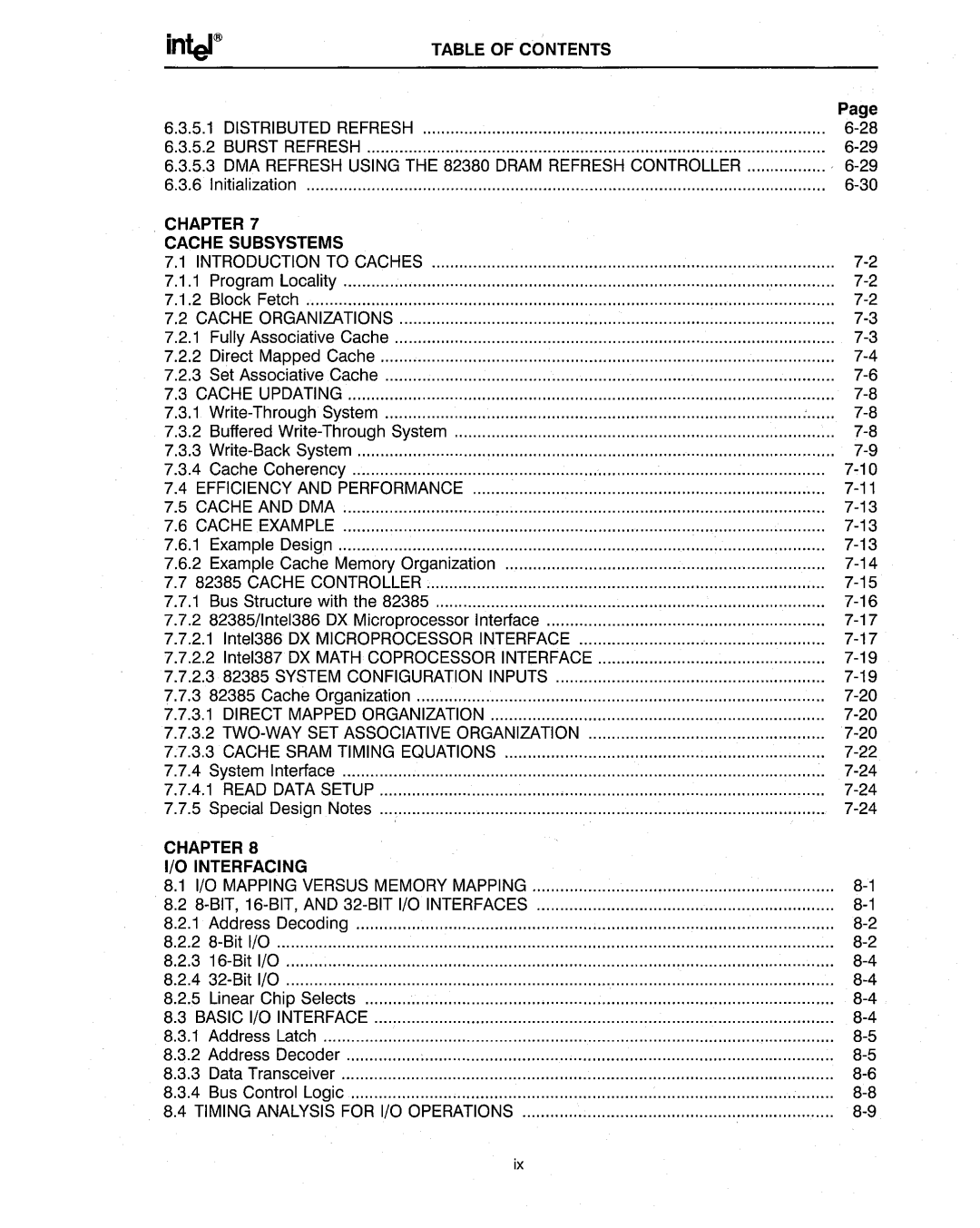

TABLE OF CONTENTS

|

|

|

| Page |

6.3.5.1 DISTRIBUTED REFRESH | ; | |||

6.3.5.2 BURST REFRESH |

| |||

6.3.5.3 DMA REFRESH USING THE 82380 DRAM REFRESH CONTROLLER | ||||

6.3.6 | Initialization | |||

. CHAPTER 7 |

|

|

| |

CACHE SUBSYSTEMS |

|

|

| |

7.1 INTRODUCTION TO CACHES | ||||

7.1.1 | Program Locality |

| ||

7.1.2 | Block Fetch | |||

7.2 CACHE ORGANIZATIONS | ||||

7.2.1 | Fully Associative Cache | ............................................................................................... | ||

7.2.2 Direct Mapped Cache |

| |||

7.2.3 Set Associative Cache | ; | |||

7.3 CACHE UPDATING |

| |||

7.3.1 | : | |||

7.3.2 Buffered | ||||

7.3.3 |

| |||

7.3.4 Cache Coherency |

| |||

7.4 EFFICIENCY AND PERFORMANCE | ||||

7.5 CACHE AND DMA | , | |||

7.6 CACHE EXAMPLE | ; | |||

7.6.1 | Example Design | , | ||

7.6.2 Example Cache Memory Organization | ||||

7.7 82385 CACHE CONTROLLER | ||||

7.7.1 | Bus Structure with the 82385 | |||

7.7.2 82385/lnte1386 DX Microprocessor Interface | ||||

7.7.2.1 Intel386 DX MICROPROCESSOR INTERFACE | ||||

7.7.2.2 Intel38TDX MATH COPROCESSOR INTERFACE | ||||

7.7.2.3 82385 SYSTEM CONFIGURATION INPUTS | ||||

7.7.3 82385 Cache Organization | ||||

7.7.3.1 DIRECT MAPPED ORGANIZATION | ||||

7.7.3.2 | ||||

7.7.3.3 CACHE SRAM TIMING EQUATIONS | ||||

7.7.4 | System Interface |

| ||

7.7.4.1 READ DATA SETUP |

| |||

7.7.5 Special Design Notes ... | ; | |||

CHAPTER 8 |

|

|

| |

I/O INTERFACING |

|

|

| |

8.1 I/O MAPPING VERSUS MEMORY MAPPING | ||||

8.2 | ||||

8.2.1 | Address Decoding | .................. | ||

8.2.2 | ||||

8.2.3 | ; | |||

8.2.4 | ||||

8.2.5 | Linear Chip Selects |

| ||

8.3 BASIC I/O INTERFACE |

| |||

8.3.1 | Address Latch | : | ||

8.3.2 Address Decoder | ; | |||

8.3.3 | Data Transceiver | |||

8.3.4 | Bus Control Logic | : | ; | |

8.4 TIMING ANALYSIS FOR I/O OPERATIONS | ||||

ix