CO

00

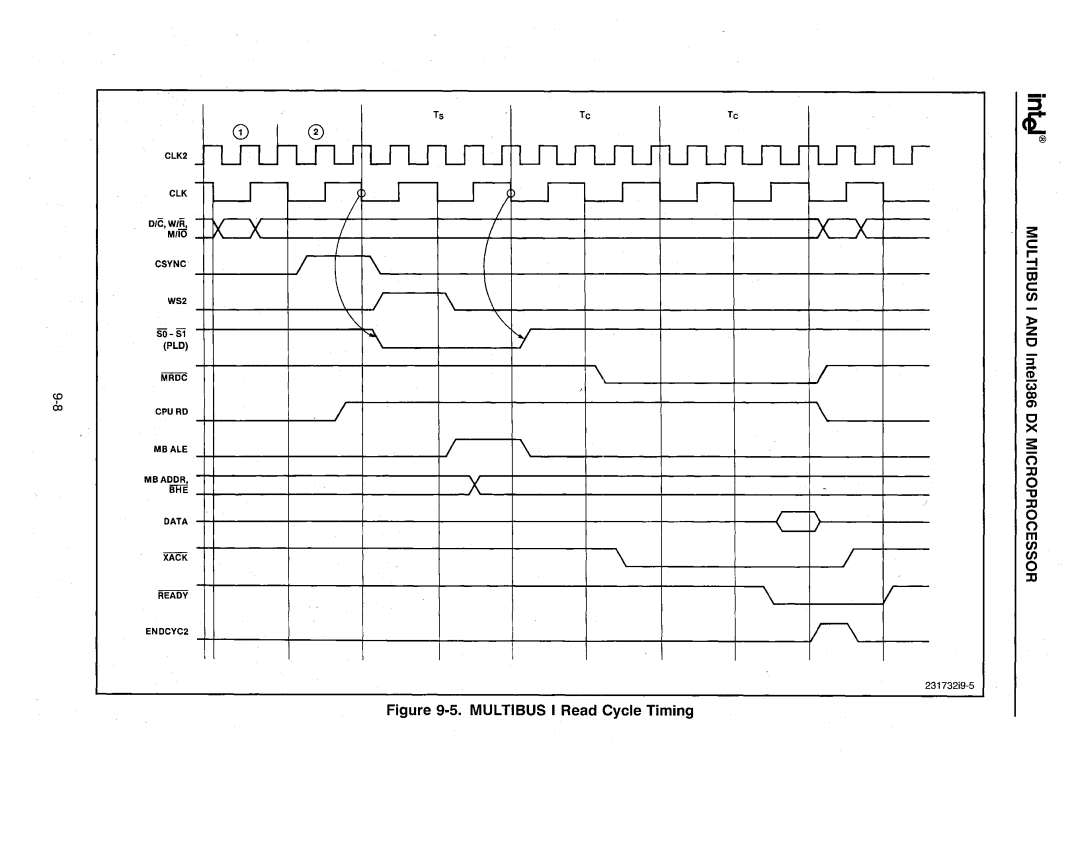

Ts'TcTc

ClK2

D/C,W/~ | - ex |

|

| |||

ClK |

|

|

| |||

|

|

|

|

| ||

MilO | - | / | I |

| t::J |

|

CSYNC |

|

|

|

|

|

|

WS2 |

| \ | \ |

|

|

|

| " |

| '" |

| ||

|

|

| ||||

| r"\ |

|

| rY |

| |

(PlD) |

|

|

|

| ||

MRDC |

|

|

|

| / |

|

CPURD |

|

|

|

|

| - |

|

|

|

|

|

| |

MBAlE |

|

|

|

|

|

|

MBADDR, |

| X |

|

| - |

|

BHE |

|

|

| , | ||

|

|

|

|

|

| |

DATA | r - "," | |

| ||

XACK |

| |

READY | V- | |

| ||

ENDCYC2 | I\ . | |

|

l

@

s:: c

~

m

c

tJ)

»

z o

CD

c;.;

CXI

0)

~

s::

o

::tI

o

"U

::tI

o

C')

m

tJ)

tJ)

o

::tI