LOCAL BUS INTERFACE

UNLOCKED lOCKED lOCKED UNLOCKED

BUS CYCLE BUS CYCLE BUS CYCLE BUS CYCLE

ClK

lOCK#

NA#

READY#

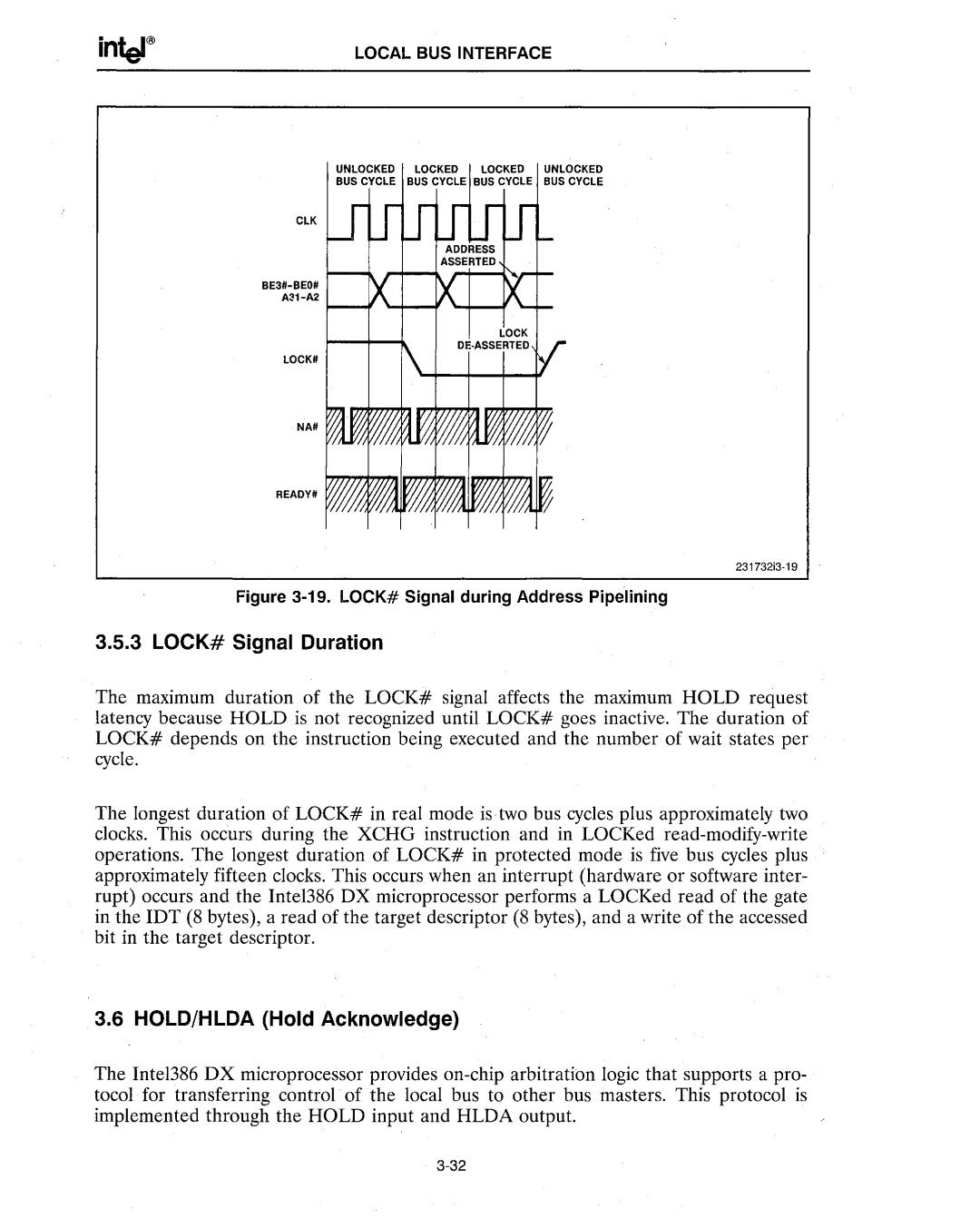

Figure 3-19. LOCK# Signal during Address Pipelining

3.5.3 LOCK# Signal Duration

The maximum duration of the LOCK# signal affects the maximum HOLD request latency because HOLD is not recognized until LOCK# goes inactive. The duration of LOCK# depends on the instruction being executed and the number of wait states per cycle.

The longest duration of LOCK# in real mode is two bus cycles plus approximately two clocks. This occurs during the XCHG instruction and in LOCKed

3.6 HOLD/HLDA (Hold Acknowledge)

The Inte1386 DX microprocessor provides