CHAPTER 7

CACHE SUBSYSTEMS

Operating at 33 MHz, the Inte1386 DX microprocessor can perform a complete bus cycle in only 60 nanoseconds, for a maximum bandwidth of 66 megabytes per second. To sustain this maximum speed, the Intel386 DX microprocessor must be matched with a

Traditional memory systems have been implemented with dynamic RAMs (DRAMs), which provide a large amount of memory for a small amount of board space and money. However,

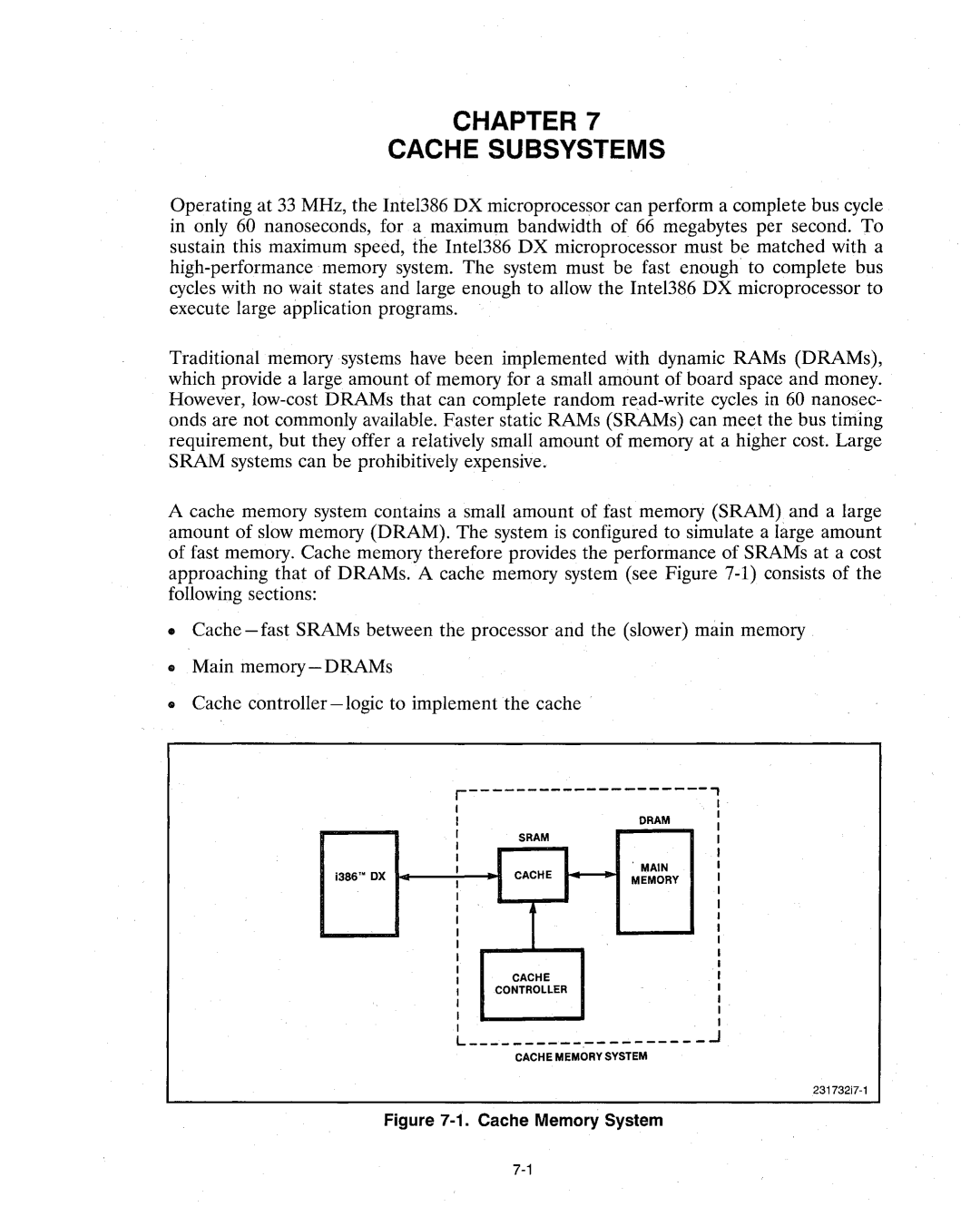

A cache memory system contains a small amount of fast memory (SRAM) and a large amount of slow memory (DRAM). The system is configured to simulate a large amount of fast memory. Cache memory therefore provides the performance of SRAMs at a cost approaching that of DRAMs. A cache memory system (see Figure

..

.. Main

.. Cache controller

r | ||

| DRAM | |

| SRAM | |

1386'· OX | . MAIN | |

CACHE 1- MEMORY | ||

| ||

| t | |

| CACHE | |

| CONTROLLER |

L ____________________

CACH E MEMORY SYSTEM