MULTIBUS I AND Intel386 DX MICROPROCESSOR

Inverting address latches convert the Inte1386 DX microprocessor address outputs to the

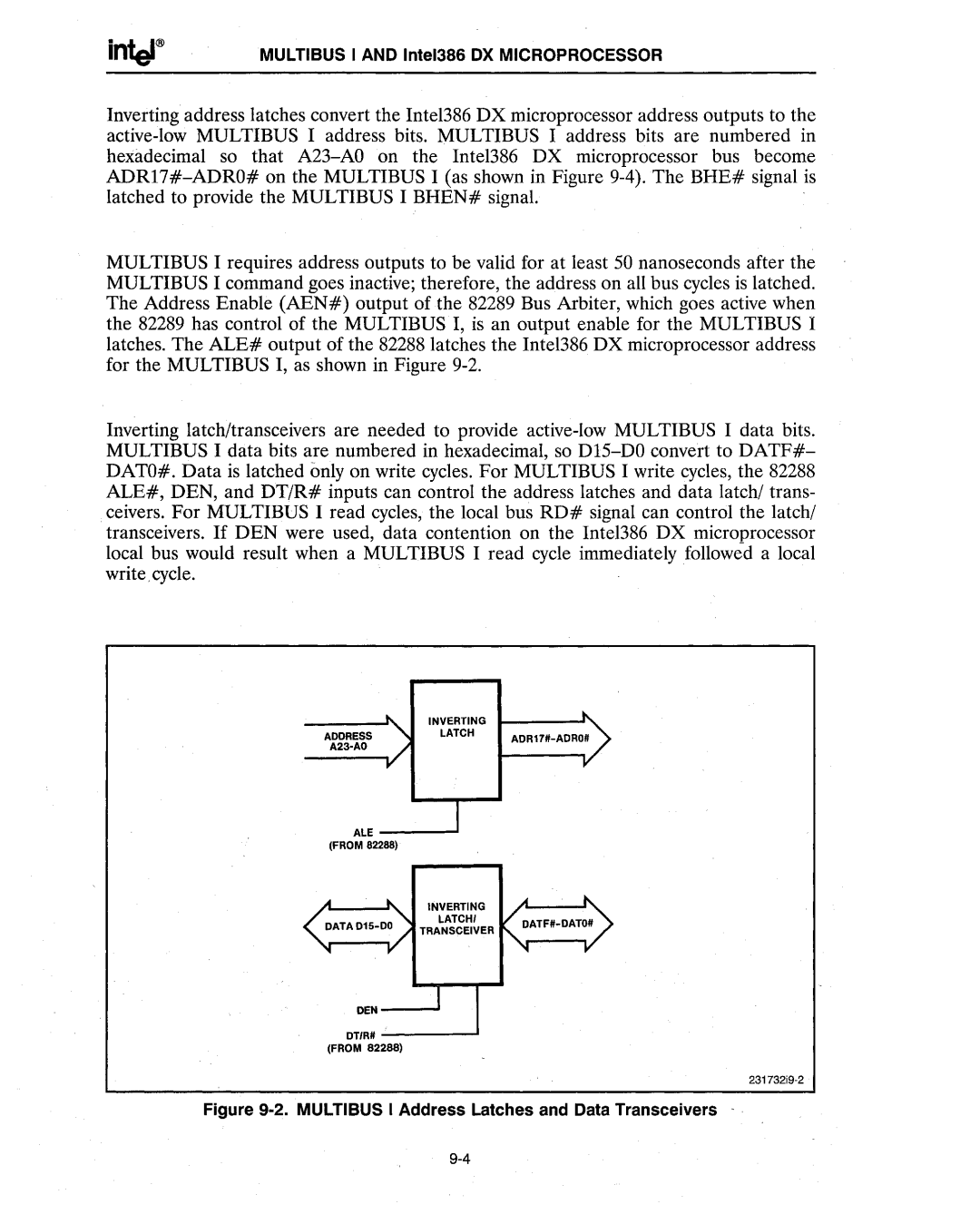

MULTIBUS I requires address outputs to be valid for at least 50 nanoseconds after the MULTIBUS I command goes inactive; therefore, the address on all bus cycles is latched. The Address Enable (AEN#) output of the 82289 Bus Arbiter, which goes active when the 82289 has control of the MULTIBUS I, is an output enable for the MULTIBUS I latches. The ALE# output of the 82288 latches the Inte1386 DX microprocessor address for the MULTIBUS I, as shown in Figure

Inverting latch/transceivers are needed to provide

.ceivers. For MULTIBUS I read cycles, the local bus RD# signal can control the latch/ transceivers. If DEN were used, data contention on the Intel386 DX microprocessor local bus would result when a MULTIBUS I read cycle immediately followed a local write, cycle.

INVERTING

ADDRESSLATCH

ALE

(FROM 82288)'

INVERTING

LATCHI

TRANSCEIVER

DEN

DTIRH . : .

(FROM 82288)