in.teI® |

|

| TABLE OF CONTENTS |

|

|

|

|

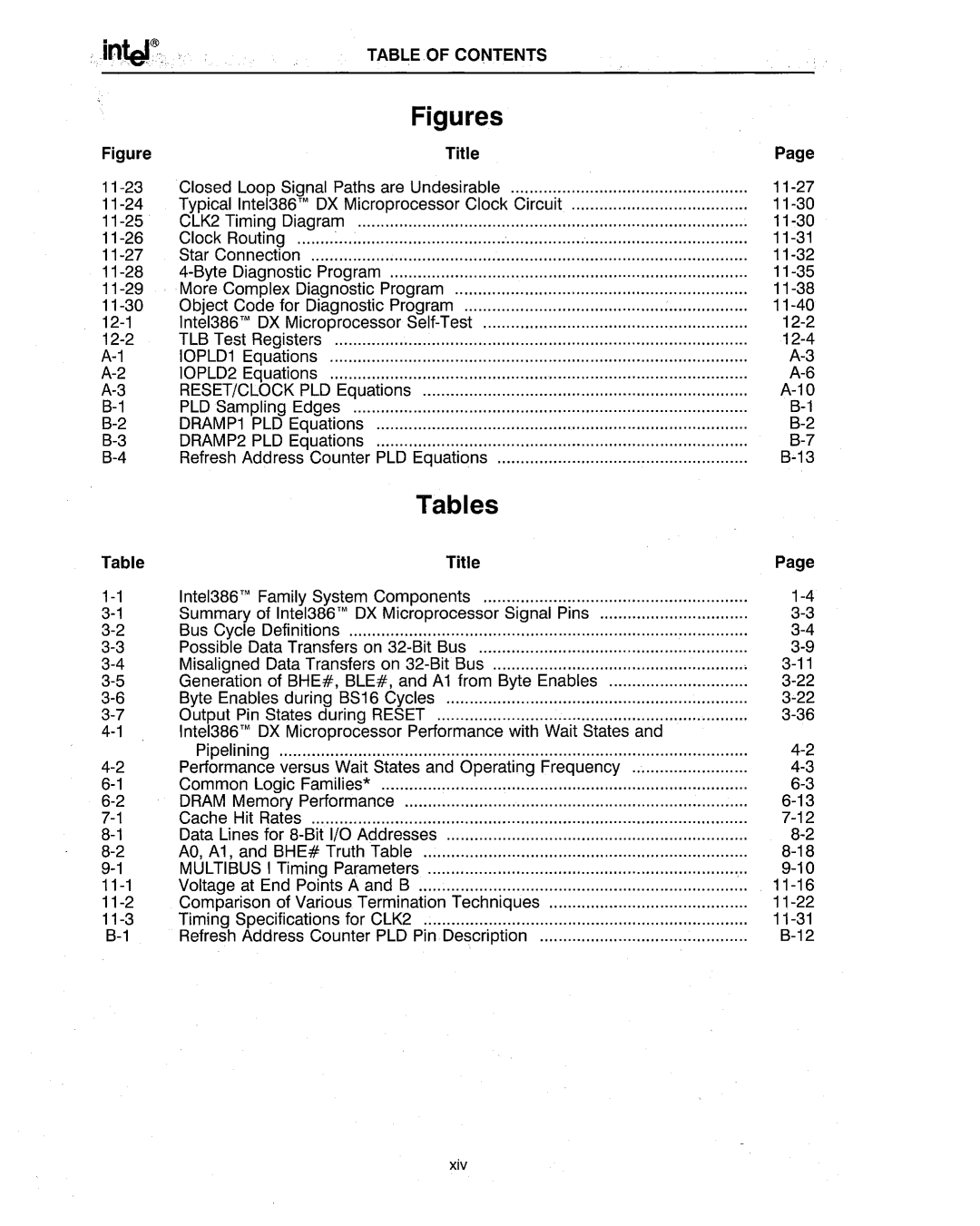

| Figures |

|

|

Figure |

|

| Title |

| Page |

Closed Loop Signal Paths are Undesirable | |||||

Typical Intel386™ | OX Microprocessor Clock Circuit | ||||

CLK2 Timing Diagram | |||||

Clock Routing | : | ||||

Star Connection | . | ||||

More Complex Diagnostic Program | |||||

Object Code for Diagnostic Program | |||||

Intel386™ | OX Microprocessor | ||||

TLB Test Registers | |||||

IOPLD1 Equations | |||||

IOPLD2 Equations | |||||

RESET/CLOCK PLD Equations | |||||

PLD Sampling Edges | |||||

DRAMP1 PLD Equations | |||||

DRAMP2 PLD Equations | |||||

Refresh Address Counter PLD Equations | |||||

|

|

| Tables |

|

|

Table |

|

| Title |

| Page |

Intel386™ | Family System Components | , | |||

Summary of Intel386™ OX Microprocessor Signal Pins | |||||

Bus Cycle Definitions | |||||

Possible Data Transfers on | |||||

Misaligned Data Transfers on | |||||

Generation of BHE#, BLE#, and Ai from Byte Enables | |||||

Byte Enables during BS16 Cycles | |||||

Output Pin States during RESET | |||||

Intel386™ | OX Microprocessor Performance with Wait States and |

| |||

| Pipelining | . | |||

Performance versus Wait States and Operating Frequency | |||||

Common Logic Families* | |||||

DRAM Memory Performance | |||||

Cache Hit Rates | . | ||||

Data Lines for | |||||

AO, Ai, and BHE# Truth Table | |||||

MULTIBUS I Timing Parameters | |||||

Voltage at End Points A and B | |||||

Comparison of Various Termination Techniques | |||||

Timing Specifications for CLK2 | |||||

Refresh Address Counter PLD Pin Description | |||||

xiv