TEST CAPABILITIES

3112 115 4o '

~------------~--~~~~~

LINEAR ADDRESS | TAG | LOOKUP/ |

|

| WRITEN |

| COMMAND REGISTER |

|

31 | 12 | 11 | 5 | 4 | 3 | 2 | 1 | 0 |

|

| ~I |

|

|

| |||

| PHYSICAL ADDRESS |

|

|

| MIT/REPLACEMENT |

| ||

|

|

|

|

| MISS POINTER |

| ||

| DATA REGISTER |

|

|

| OR |

|

| |

|

|

| REPLACEMENT BIT |

| ||||

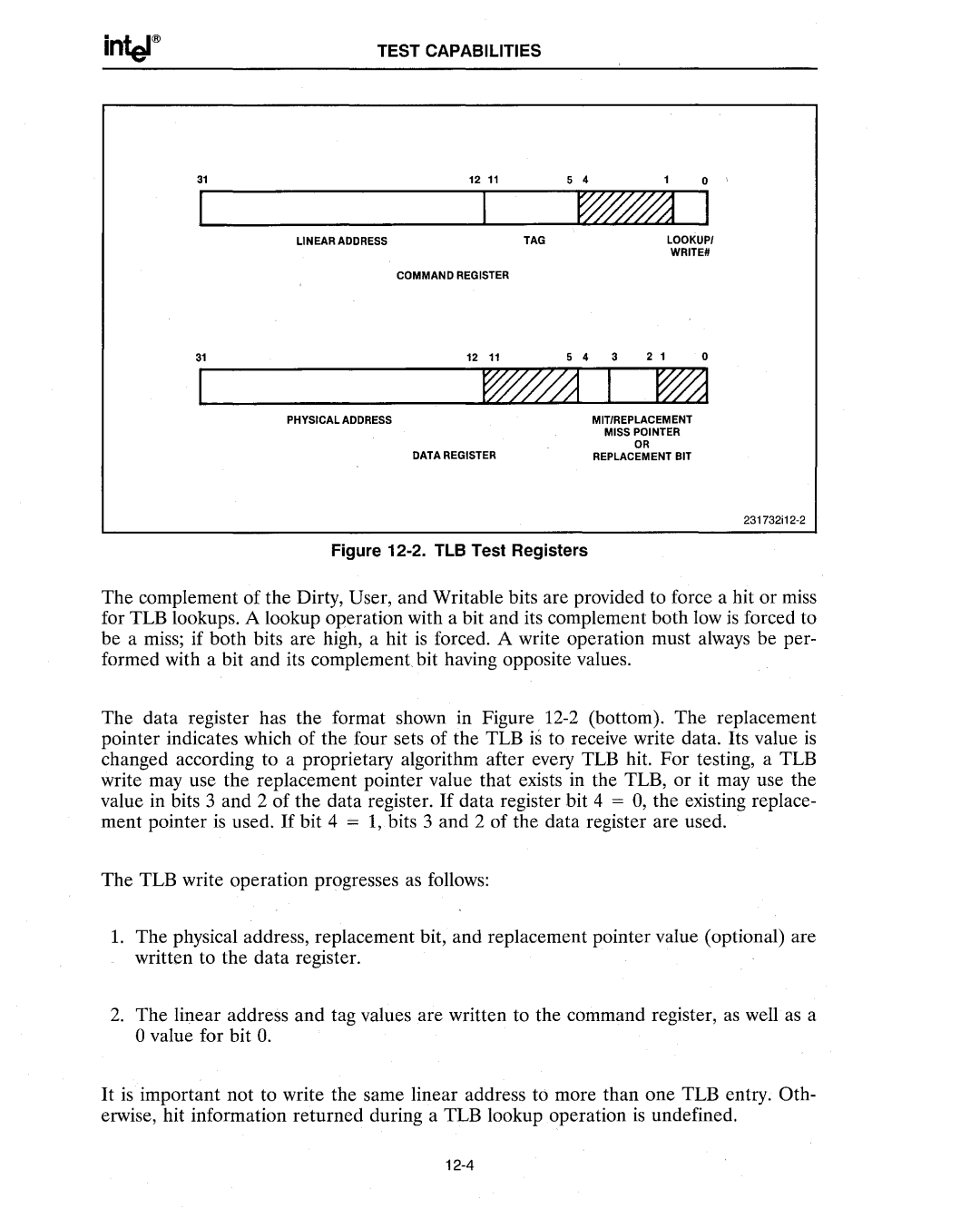

Figure 12-2. TLB Test Registers

The complement of the Dirty, User, and Writable bits are provided to force a hit or miss for TLB lookups. A lookup operation with a bit and its complement both low is forced to be a miss; if both bits are high, a hit is forced. A write operation must always be per- formed with a bit and its complement bit having opposite values.

The data register has the format shown in Figure

The TLB write operation progresses as follows:

1.The physical address, replacement bit, and replacement pointer value (optional) are written to the data register.

2.The linear address and tag values are written to the command register, as well as a ovalue for bit O.

It is important not to write the same linear address to more than one TLB entry. Oth- erwise, hit information returned during a TLB lookup operation is undefined.