CACHE SUBSYSTEMS

32·BIT | 31 |

|

|

|

|

|

|

|

|

| |

PROCESSOR | SELECT |

| INDEX |

|

|

ADDRESS |

|

|

| ||

|

|

|

|

| |

|

|

|

| ||

|

|

| |||

|

|

| DATA | INDEX | TAG |

|

|

|

| FFFC | l~~ |

|

|

| 11223344 | FFF8 | |

INDEX | TAG | DATA |

| 0010 | |

| OOOC | ||||

|

|

|

| ||

FFFC | 01 | 12345678 |

| OOOS | |

~ | 0004 | ||||

FFF8 | FF | 11223344 | 0000 |

| |

|

|

|

|

| |

0010 |

|

|

|

| - |

| |

|

|

|

| - |

| ||

OOOC |

| 87654321 |

|

| - |

| |

0008 | 00 | ~ | ~ | 12345678 | FFFC | ||

0004 | 01 | 11235813 | |||||

|

| FFF8 | |||||

0000 | 00 | 13579246 | - |

|

|

| |

(14 BITS) I_ | j+32BITS+j |

|

| 0010 | |||

|

| OOOC | |||||

15 BYTES |

|

|

|

| 0.008 | ||

|

|

|

| ' |

| ||

| 64KSRAM CACHE |

| 11235813 | 0004 | |||

|

|

|

|

|

| 0000 | |

|

|

|

|

|

| FFFC | |

|

|

|

|

|

| FFF8 | |

|

|

|

|

|

| 0010 | |

|

|

|

|

|

| OOOC | |

|

|

|

|

| 87654321 | 0008 | |

|

|

|

|

| 13579246 | 0004 | |

|

|

|

|

| 0000 | ||

)-

j+32BITS+j

231732i7·9

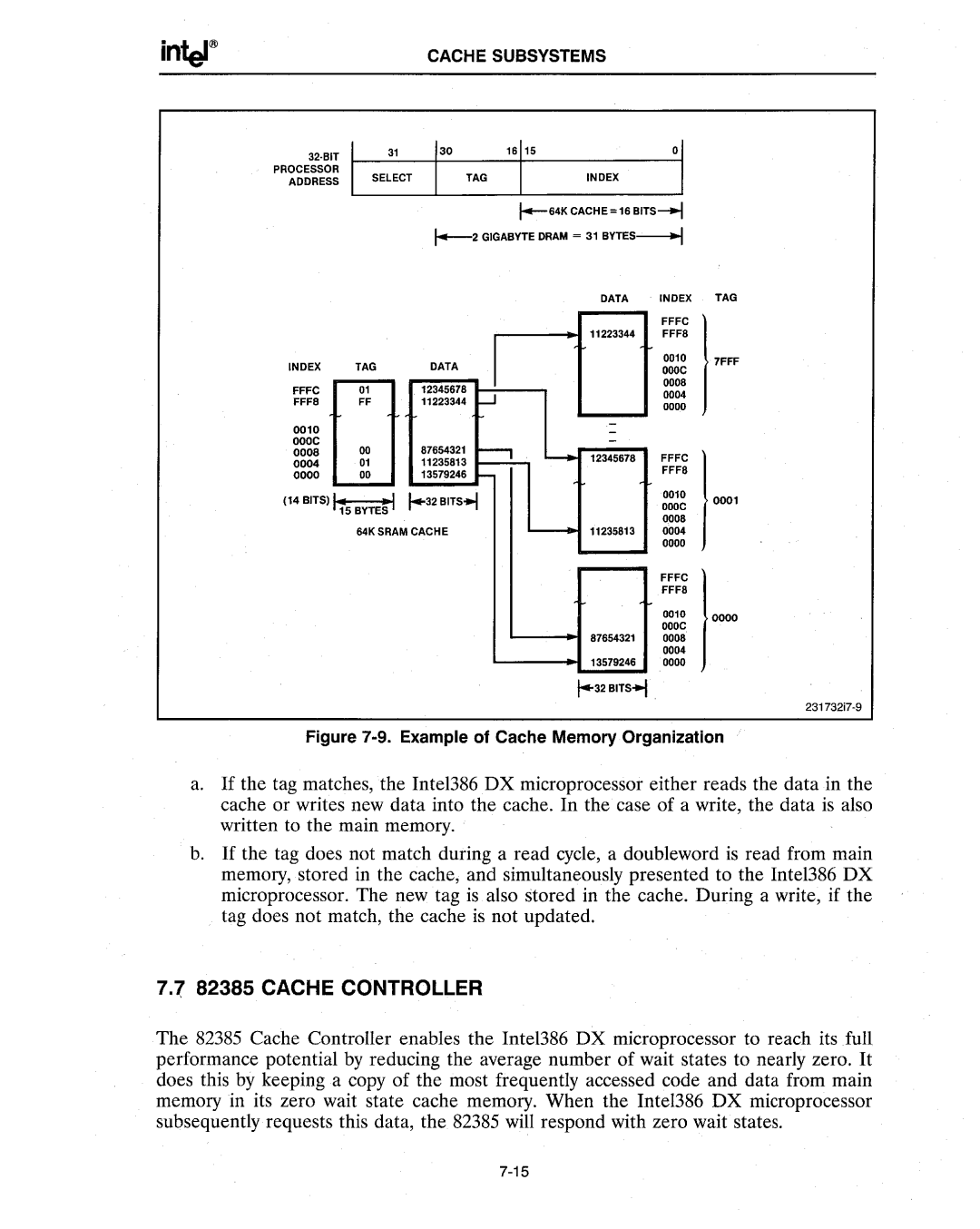

Figure 7-9. Example of Cache Memory Organization

a.If the tag matches, the Intel386 DX microprocessor either reads the data in the cache or writes new data into the cache. In the case of a write, the data is also written to the main memory.

b.If the tag does not match during a read cycle, a doubleword is read from main memory, stored in the cache, and simultaneously presented to the Intel386 DX microprocessor. The new tag is also stored in the cache. During a write, if the tag does not match, the cache is not updated.

7.., 82385 CACHE CONTROLLER

The 82385 Cache Controller enables the Inte1386 DX microprocessor to reach its full performance potential by reducing the average number of wait states to nearly zero. It does this by keeping a copy of the most frequently accessed code and data from main memory in its zero wait state cache memory. When the Intel386 DX microprocessor subsequently requests this data, the 82385 will respond with zero wait states.