TABLE OF CONTENTS

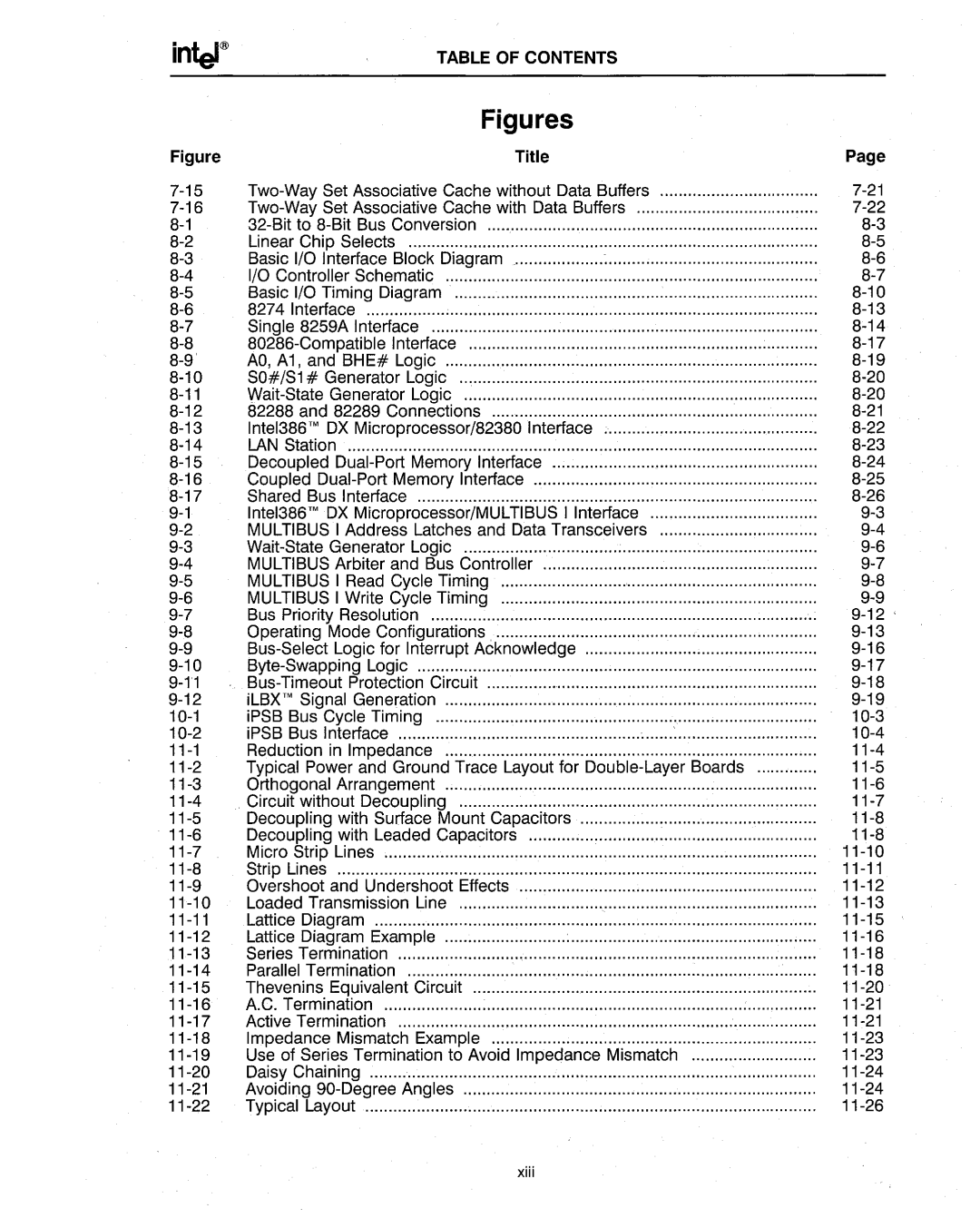

Figures

Figure |

|

|

| Title |

|

| Page |

| . | ||||||

Linear Chip Selects |

|

| . | ||||

Basic I/O Interface Block Diagram | , ..................: | ||||||

I/O Controller Schematic |

|

| . | ||||

Basic I/O Timing Diagram | ............................................................................. |

| . | ||||

8274 Interface | ; |

| . | ||||

Single 8259A Interface |

|

| . | ||||

| . | ||||||

AO, A1, and BHE# Logic |

|

| . | ||||

SO#/S1 # Generator Logic |

| . | |||||

| . | ||||||

82288 and 82289 Connections |

| . | |||||

Intel386™ | DX Microprocessor/82380 Interface | .............................................. | |||||

LAN Station |

|

| . | ||||

Decoupled | . | ||||||

Coupled | . | ||||||

Shared Bus Interface |

|

| . | ||||

Intel386™ | DX Microprocessor/MULTIBUS I Interface | ||||||

MULTIBUS I Address Latches and Data Transceivers | |||||||

| . | ||||||

MULTIBUS Arbiter and Bus Controller | . | ||||||

MULTIBUS I Read Cycle Timing |

| ' | |||||

MULTIBUS I Write Cycle Timing |

| . | |||||

Bus Priority Resolution |

|

| . | ||||

Operating Mode Configurations |

| , | |||||

........................ | ; | ||||||

|

| . | |||||

| . | ||||||

iLBXTM Signal Generation |

|

| . | ||||

iPSB Bus Cycle Timing | , | ||||||

iPSB Bus Interface |

|

| ~ | ||||

Reduction in Impedance |

|

| . | ||||

Typical Power and Ground Trace Layout for | |||||||

Orthogonal Arrangement |

|

| . | ||||

. Circuit without Decoupling | .................................................................... |

| , | ||||

Decoupling with Surface Mount Capacitors | ................................................... | ||||||

Decoupling with Leaded Capacitors | ;... | , | |||||

Micro Strip Lines |

|

| . | ||||

Strip Lines | ...................................................................................................... |

|

| . | |||

Overshoot and Undershoot Effects | ............................................................... | . | |||||

Loaded Transmission Line | ............................... |

| , | ||||

Lattice Diagram | , | ||||||

Latt.ice Diag~am.Example | ~ | . | |||||

Senes Termination |

|

| . | ||||

Parallel Termination | ' | ; | : | ||||

Thevenins Equivalent Circuit |

| . | |||||

A.C. Termination |

|

| ; | ||||

Active Termination |

|

| . | ||||

Impedance Mismatch Example |

| . | |||||

Use of Series Termination to Avoid Impedance Mismatch | |||||||

Daisy Chaining |

|

| . | ||||

Avoiding |

| . | |||||

Typical Layout ' |

|

| . | ||||

xiii